Gpio, Clock, Table 6-1 gpio pins – ADLINK aTCA-N700 User Manual

Page 32

aTCA-N700 HW Users Guide

32

6.10. GPIO

The GPIO pins are arranged on the board as shown in Table 6-1. The CPLD is responsible

for the interfaces between the NPs and the LMP. Some of such interfaces depend on the

GPIO connections to the CPLD, which may be used as I/O mapping on to the CPLD registers

so that the LMP or the NPs can perform read/write operations to the other end. Interrupt

forwarding from the NPs to the LMP is an example on using GPIO-to-CPLD connections.

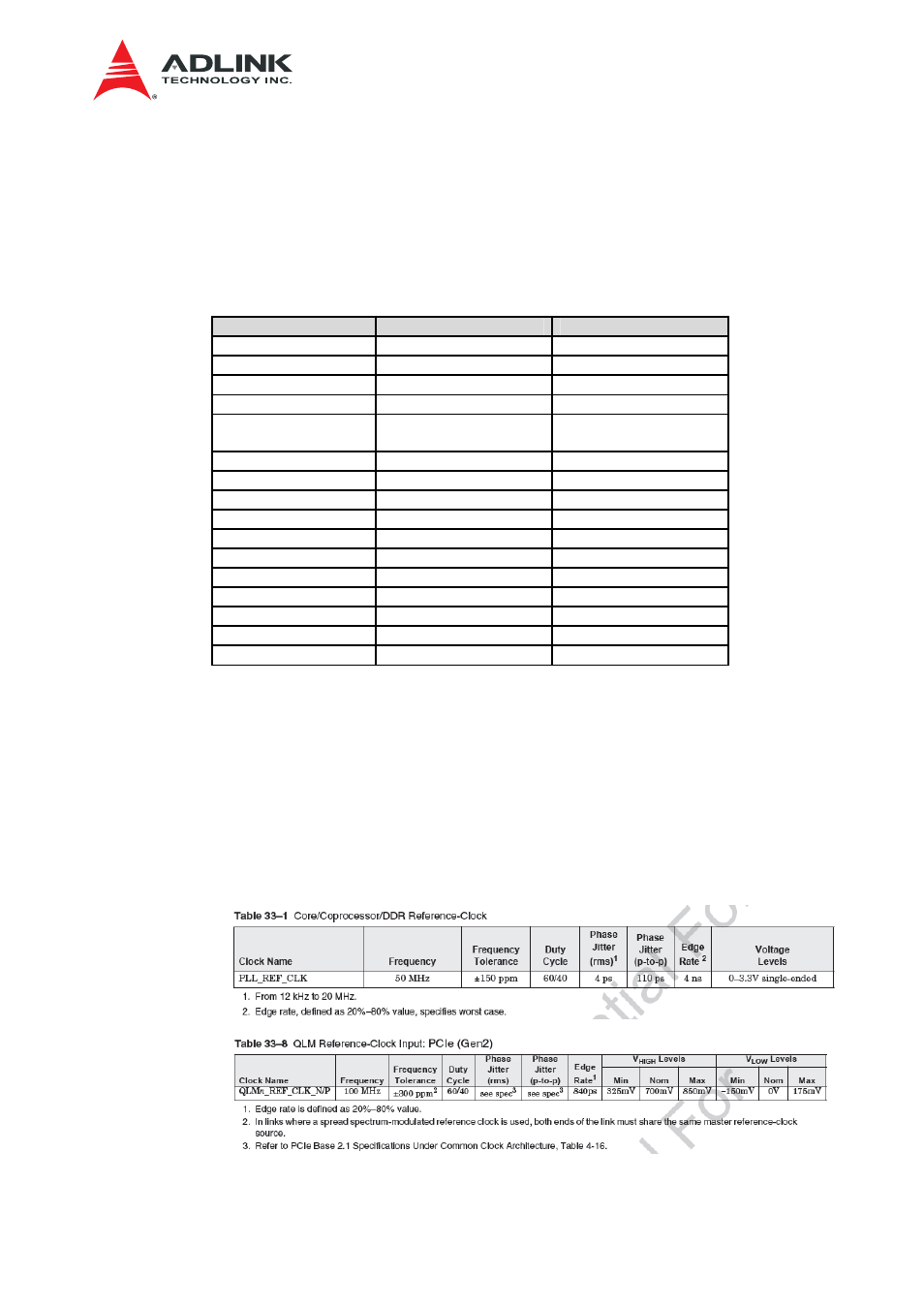

Table 6-1 GPIO Pins

Signal Name

Description

Setting Value

GPIO0

Connected to CPLD

Reserved

GPIO1

Connected to CPLD

Reserved

GPIO2

Connected to CPLD

Reserved

GPIO3

Connected to CPLD

Reserved

GPIO4

EVENT of DIMM

Memory

DIMM Memory Event

Input

GPIO5

Connected to CPLD

Reserved

GPIO6

Connected to CPLD

Reserved

GPIO7

Connected to CPLD

Reserved

GPIO8

Connected to CPLD

Reserved

GPIO9

Connected to CPLD

Reserved

GPIO10

Connected to CPLD

Reserved

GPIO11

Connected to CPLD

Reserved

GPIO12

Connected to CPLD

Reserved

GPIO13

Connected to CPLD

Reserved

GPIO14

Connected to CPLD

Reserved

GPIO15

Connected to CPLD

Reserved

6.11. Clock

The CN6800 has a single reference-clock signal (PLL_REF_CLK, 50MHz) that feeds into

three PLLs: Core PLL, Coprocessor PLL, and DDR PLL) that provide the clock signals for the

rest of the chip.

Also, the clocks fed externally on the blade include: QLM reference (PCIe Gen2), QLM

reference (ILK), QLM reference (XAUI), QLM reference (RXAUI/DXAUI) and RGMII reference

clocks. Their requirements are copied to Figure 6-12 from the datasheet, respectively. The

on-board clock tree is described in Section 11 .