I/o ports, Table 9-2 ipmc pin map and on-board arrangement – ADLINK aTCA-N700 User Manual

Page 56

aTCA-N700 HW Users Guide

56

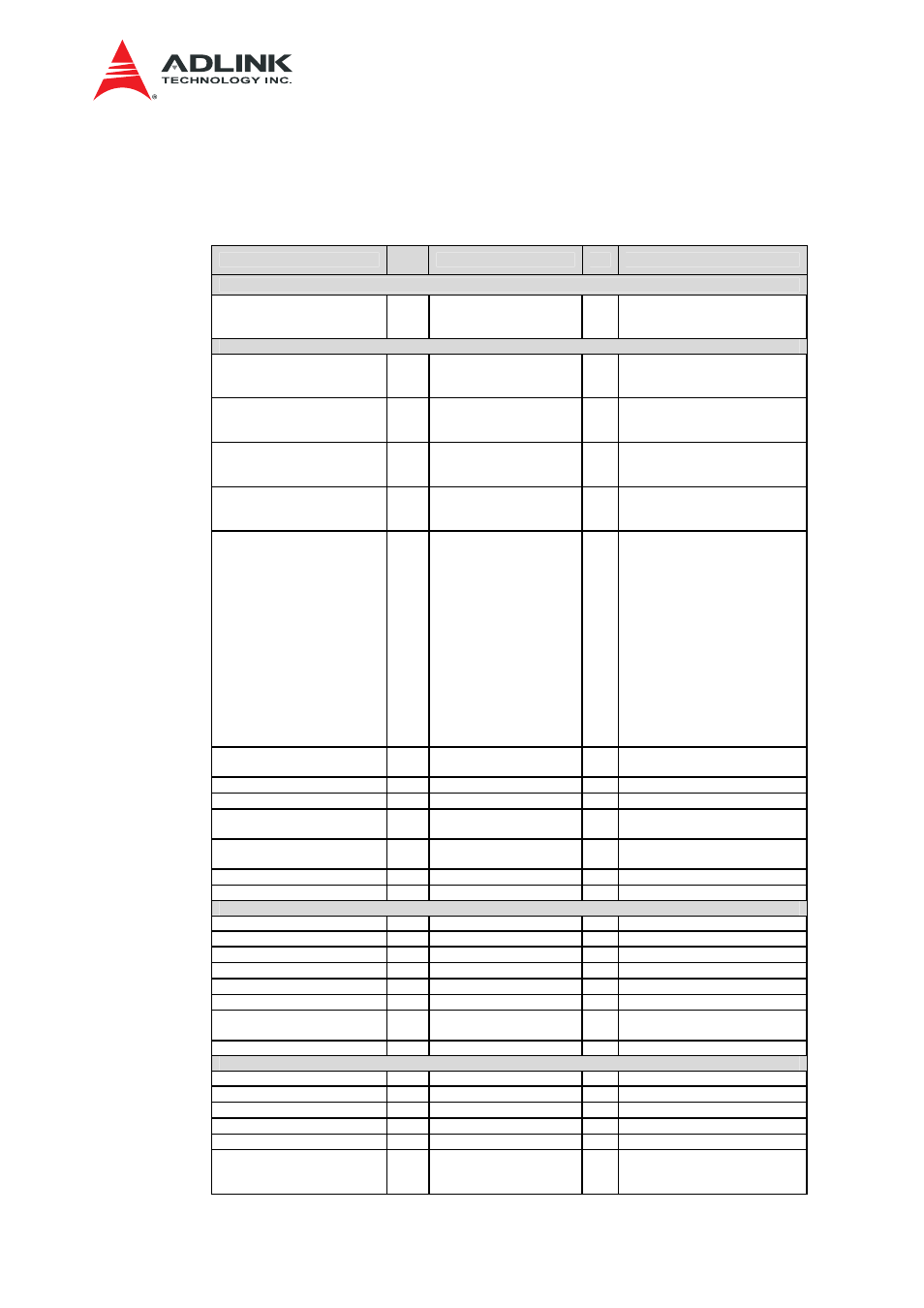

9.2. I/O Ports

Due to the nature of the blade management, the IPMC is equipped with the many I/O

ports that are configurable. Table 9-2 illustrates most of the I/O ports and connections

on the blade.

Table 9-2 IPMC Pin map and on-board arrangement

Pin Name

Pin

No.

Connection

I/O

Description

MSS I/O

MSS_RESET_N R1

IPMC_MSS_RESET_L

I

Core Reset

0 : Reset

1 : Normal operating

I2C Interface

I2C_0_SDA_GPIO_22 V21

IPMC_IPMBA_SDA

- Connected to Zone 1

Connector via I2C Buffer

I/O

IPMB_A I2C Address/data

signal

I2C_0_SCL_GPIO_23 U21

IPMC_IPMBA_SCL

- Connected to Zone 1

Connector via I2C Buffer

I

IPMB_A I2C Clock signal

I2C_1_SDA_GPIO_30 U20

IPMC_IPMBB_SDA

- Connected to Zone 1

Connector via I2C Buffer

I/O

IPMB_B I2C address/data

signal

I2C_1_SCL_GPIO_31 V22

IPMBC_IPMBB_SCL

- Connected to Zone 1

Connector via I2C Buffer

I

IPMB_B I2C Clock signal

GPIO_0_IO47RSB4V0 V1

IPMC_MO_SCL

O

IPMI I2C Clock signal for I2C

Devices

I2C Address(Base)

- M24256 :

0x1010010X(SDR/SEL)

- M24256 :

0x1010001X(COLD/NV Data)

- DS75 : 0x1001000X

- PIM400 : 0x0101000x

- MAX11605 : 0x1100101X

(0 : MSW_1V0, 1 :

MSW_AVS, 2 : SW_1V2, 3 :

1V5, 4 : LMP_1V0, 5 :

LMP_VTT, 6 : RTC_VAT, 7 :

IPMC_1V5)

GPIO_1_IO46_RSB4V0 R3

IPMC_MO_SDA

I/O

IPMI I2C Address/data signal

I2C Address for I2C Devices

GPIO_2_IO45RSB4V0 W1

NC

O

Not

used

GPIO_3_IO44RSB4V0 Y1

NC

O

Not

used

GPIO_4_IO43RSB4V0 AA1

IPMB_L_SCL1

O

IPMB-L I2C Clock signal for

RTM

GPIO_7_IO40RSB4V0 W2

IPMB_L_SDA1

I/O

IPMB-L I2C Address/Data

signal for RTM

GPIO_5_IO42RSB4V0 U2

NC

O

Not

used

GPIO_6_IO41RSB4V0 V2

NC

O

Not

used

SPI Interface

SPI_0_DO_GPIO_16

U17

IPMC_SPI0_DO

O

SPI Data Output

SPI_0_DI_GPIO_17

V18

IPMC_SPI0_DI

I

SPI Data Input

SPI_0_CLK_GPIO_18

W19

IPMC_SPI0_CLK

O

SPI Clock output

SPI_0_SS_GPIO_19

Y20

IPMC_SPI0_nSS

O

SPI Chip select

SPI_1_DO_GPIO_24 T17

NC

O

Not

used

SPI_1_DI_GPIO_25 V19

NC

O

Not

used

SPI_1_CLK_GPIO_26

AA2

2

NC O

Not

used

SPI_1_SS_GPIO_27 W21

NC

O

Not

used

JTAG Interface

TMS

P20

IPMC_JTAG_TMS

I

JTAG Test mode select

TCK

P18

IPMC_JTAG_TCK

I

JTAG Test clock

TDI

P17

IPMC_JTAG_TDI

I

JTAG Test Data Input

TRSTB

P22

IPMC_JTAG_nTRST

I

JTAG Test Reset

TDO

P21

IPMC_JTAG_TDO

O

JTAG Test Data Output

JTAGSEL

R16

J8 2 PIN Jumper conn

I

JTAG Enable Select

0 : JTAG Mode

1 : Normal Mode