Ipmc, Table 9-1 a2f500 features – ADLINK aTCA-N700 User Manual

Page 55

aTCA-N700 HW Users Guide

55

9.1. IPMC

The SmartFusion cSOC A2F500 is made by integrating FPGA technology with

programmable high performance analog and hardened ARM Cortex-M3 microcontroller

blocks on a flash semiconductor process. The three key building blocks include:

Microcontroller Subsystem (MSS), Programmable Analog, and ProASIC3 FPGA Fabric.

The MSS is composed of a 100 MHz Cortex-M3 processor and integrated peripherals,

which are SPI, I2C, and UART serial ports, embedded FlashROM (EFROM), 10/100

Ethernet MAC, timers, PLLs, oscillators, RTC, and peripheral DMA controller. The

Programmable Analog Subsystem has Analog Front-End (AFE) and Analog Compute

Engine (ACE). The ProASIC3 FPGA Fabric gives benefits from the advantages only

flash-based devices offer such as reduced cost of ownership, low power and security.

The features of the IPMC A2F500 are summarized in Table 9-1.

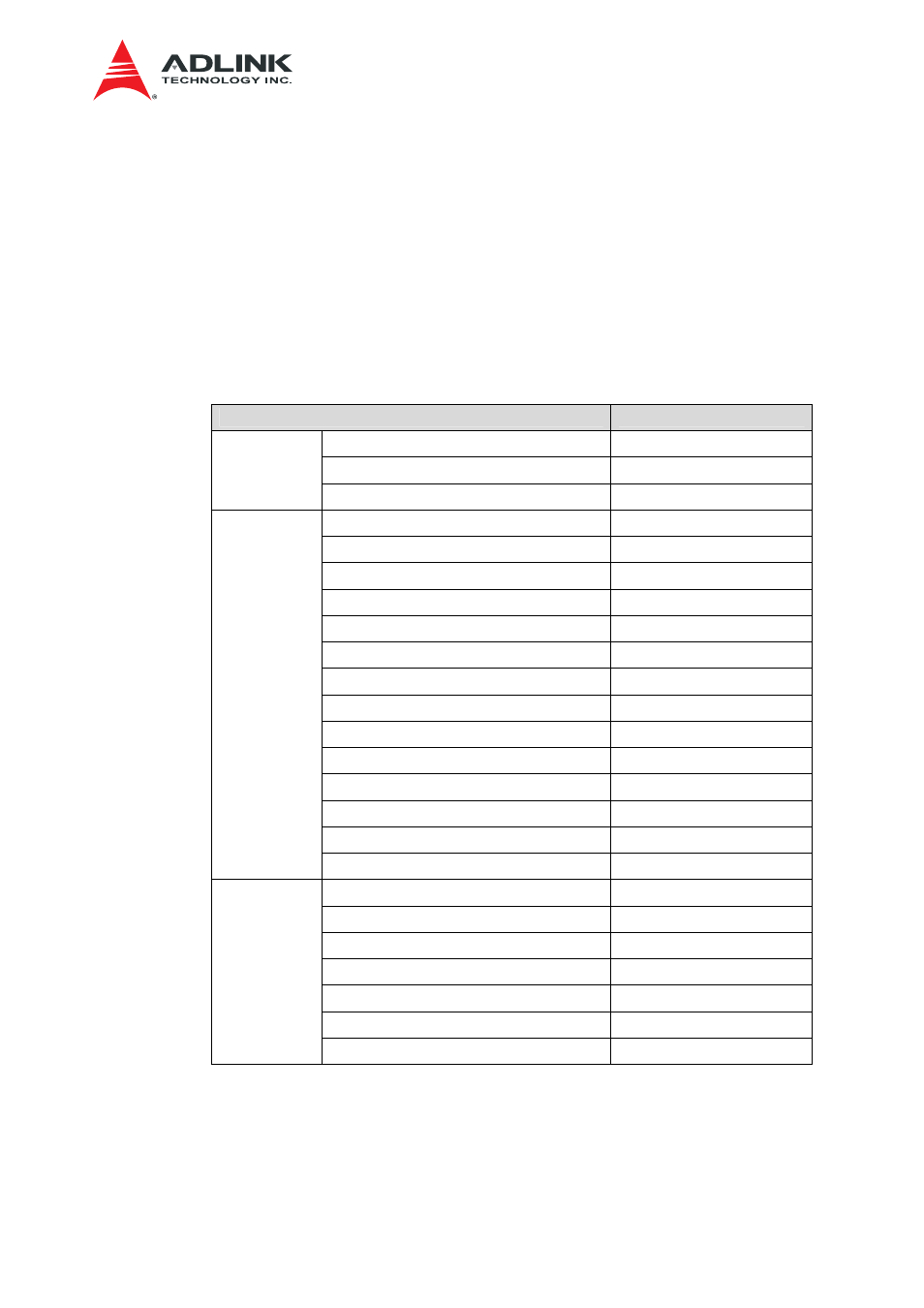

Table 9-1 A2F500 Features

SmartFusion Device Feature

A2F500

System Gates

500,000

Tiles (D-flip-flops)

11,520

FPGA Fabric

RAM Blocks (4,608 bits)

24

Flash (Kbytes)

512

SRAM (Kbytes)

64

Cortex-M3 with memory protection unit (MPU)

Yes

10/100 Ethernet MAC

Yes

External Memory Controller (EMC)

24-bit address,16-bit data

DMA

8 Ch

I2C

2

SPI

2

16550 UART

2

32-Bit Timer

2

PLL

2

32 KHz Low Power Oscillator

1

100 MHz On-Chip RC Oscillator

1

Microcontroller

Subsystem

(MSS)

Main Oscillator (32 KHz to 20 MHz)

1

ADCs (8-/10-/12-bit SAR)

3

DACs (12-bit sigma-delta)

3

Signal Conditioning Blocks (SCBs)

5

Comparators2

10

Current Monitors2

5

Temperature Monitors2

5

Programmable

Analog

Bipolar High Voltage Monitors2

10

The operating system on embedded ARM processor is FreeRTOS, which is a portable,

open source, royalty free, mini real-time kernel (www.freertos.org). Most essential

driver packages are available from the SmartFusion SDK.