I2c serial bus interface, C serial bus interface – GW Instek GDS-2000A series Option User Manual User Manual

Page 56

GDS-2000A Series Options Manual

56

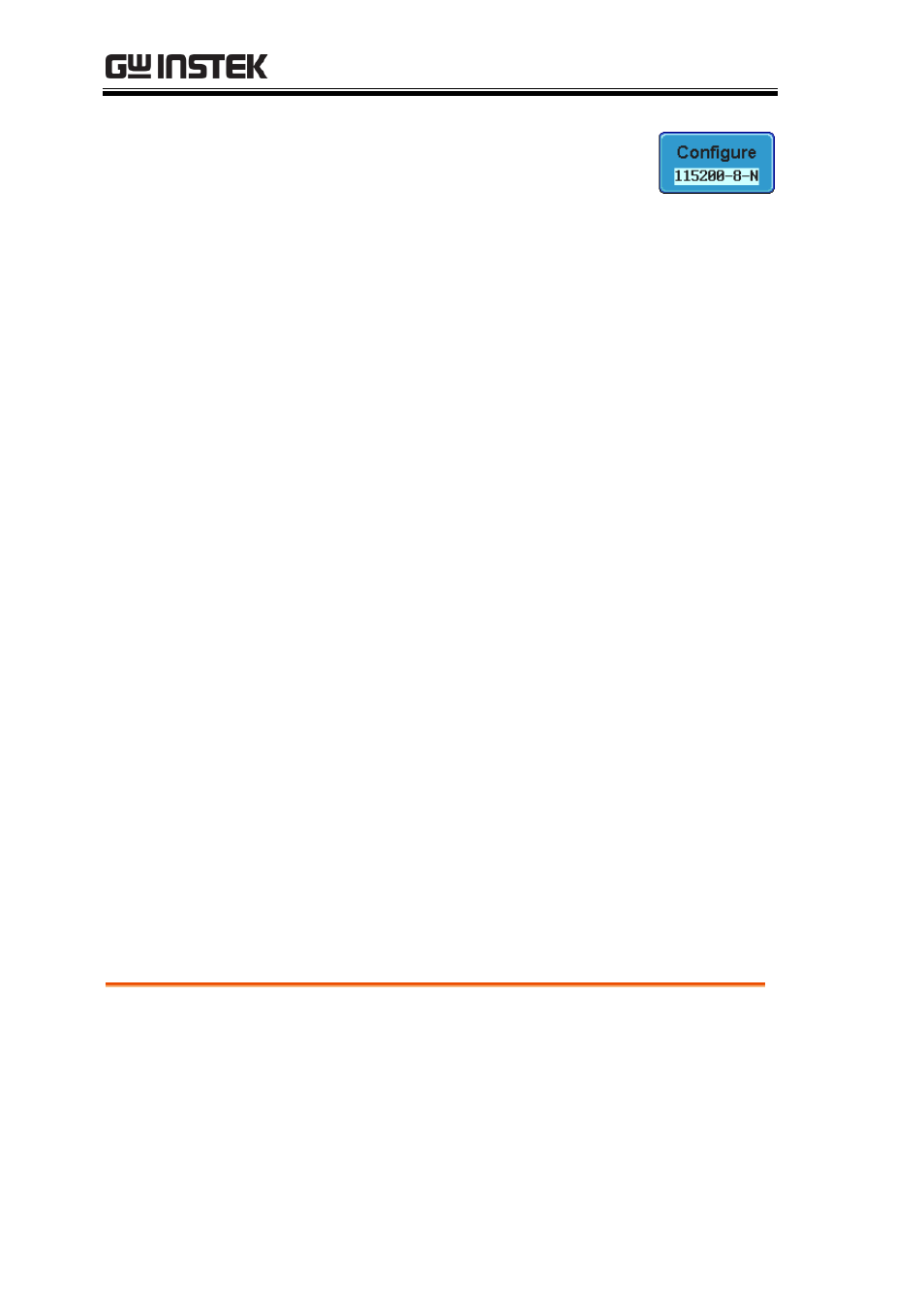

1. Press Configure from the bottom

menu.

2. From the side menu select the Baud rate, Data

bits, Parity, Packets and End of Packet bits.

Baud Rate

50, 75, 110, 134, 150, 300, 600, 1200,

1800, 2000, 2400, 3600, 4800, 7200,

9600, 14400, 15200, 19200, 28800,

31250, 38400, 56000, 57600, 76800,

115200, 128000, 230400, 460800,

921600, 1382400, 1843200, 2764800

Data Bits

8 (fixed)

Parity

Odd, Even, None

Packets

On, Off

End of

Packet

(Hex)

00(NUL), OA(LF), OD(CR), 20(SP),

FF

I

2

C Serial Bus Interface

The I

2

C bus is a 2 wire interface with a serial data line (SDA) and

serial clock line (SCLK). The I

2

C protocol supports 7 or 10 bit

addressing and multiple masters. The decode software will trigger

on any of the following conditions: a start/stop condition, a restart,

a missing acknowledge message, Address, Data or Address&Data

frames. The I

2

C trigger can be configured for 7 or 10 bit addressing

with the option to ignore the R/W bit as well as triggering on a

data value or a specific address and direction (read or write or

both).

Panel operation

1. Connect each of the bus signals (SCLK, SDA) to

one of the logic analyzer inputs. Connect the

ground potential of the bus to the logic

analyzer’s ground probe line.