Rainbow Electronics DS2180A User Manual

Page 9

DS2180A

041995 9/36

TRANSMIT SIGNALING

When enabled (via TCR.4) channel signaling is inserted

in frames 6 and 12 (193S) or in frames 6, 12, 18 and 24

(193E) in the 8th bit position of every channel word.

Signaling data is sampled at TABCD on the falling edge

of TCLK during bit 8 of each input word during signaling

frames. Logical combination of clocks TMO, TSIGFR

and TSIGSEL allows external multiplexing of separate

serial links for A, B or A, B, C, D signaling sources.

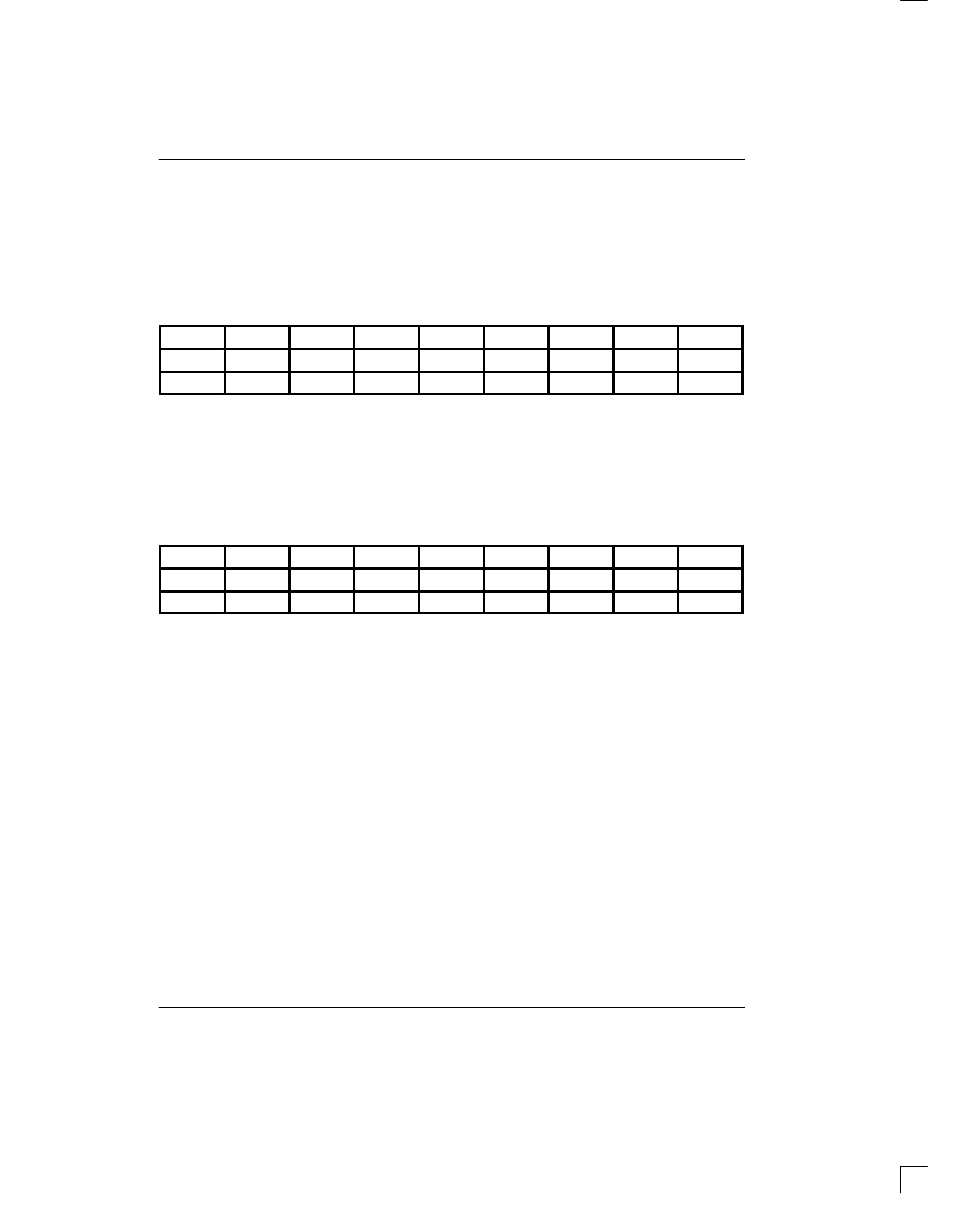

TTR1–TTR3: TRANSMIT TRANSPARENCY REGISTERS Figure 6

(MSB)

(LSB)

CH8

CH7

CH6

CH5

CH4

CH3

CH2

CH1

TTR1

CH16

CH15

CH14

CH13

CH12

CH11

CH10

CH9

TTR2

CH24

CH23

CH22

CH21

CH20

CH19

CH18

CH17

TTR3

SYMBOL

POSITION

NAME AND DESCRIPTION

CH24

TTR3.7

Transmit Transparent Registers. Each of these bit positions represents a

CH1

TTR1.0

DS0 channel in the outgoing frame. When set, the corresponding channel

is transparent.

TIR1–TIR3: TRANSMIT IDLE REGISTERS Figure 7

(MSB)

(LSB)

CH8

CH7

CH6

CH5

CH4

CH3

CH2

CH1

TIR1

CH16

CH15

CH14

CH13

CH12

CH11

CH10

CH9

TIR2

CH24

CH23

CH22

CH21

CH20

CH19

CH18

CH17

TIR3

SYMBOL

POSITION

NAME AND DESCRIPTION

CH24

TIR3.7

Transmit Idle Registers. Each of these bit positions represents a DS0

CH1

TIR1.0

channel in the outgoing frame. When set, the corresponding channel will

output an idle code format determined by TCR.2.

TRANSMIT CHANNEL TRANSPARENCY

Individual DS0 channels in the T1 frame may be pro-

grammed clear (no inserted robbed bit signaling and no

bit 7 zero suppression) by setting the appropriate bits in

the transmit transparency registers. Channel transpar-

ency is required in mixed voice/data or data-only envi-

ronments such as ISDN, where data integrity must be

maintained.

TRANSMIT IDLE CODE INSERTION

Individual outgoing channels in the frame can be pro-

grammed with idle code by asserting the appropriate

bits in the transmit idle registers. One of two idle code

formats, 7F (Hex) and FF (Hex) may be selected by the

user via TCR.3. If enabled, robbed bit signaling data is

inserted into the idle channel, unless the appropriate

TTR bit is set for that channel. This feature eliminates

external hardware currently required to intercept and

stuff unoccupied channels in the DS1 bit stream.