Rainbow Electronics DS2180A User Manual

Page 18

DS2180A

041995 18/36

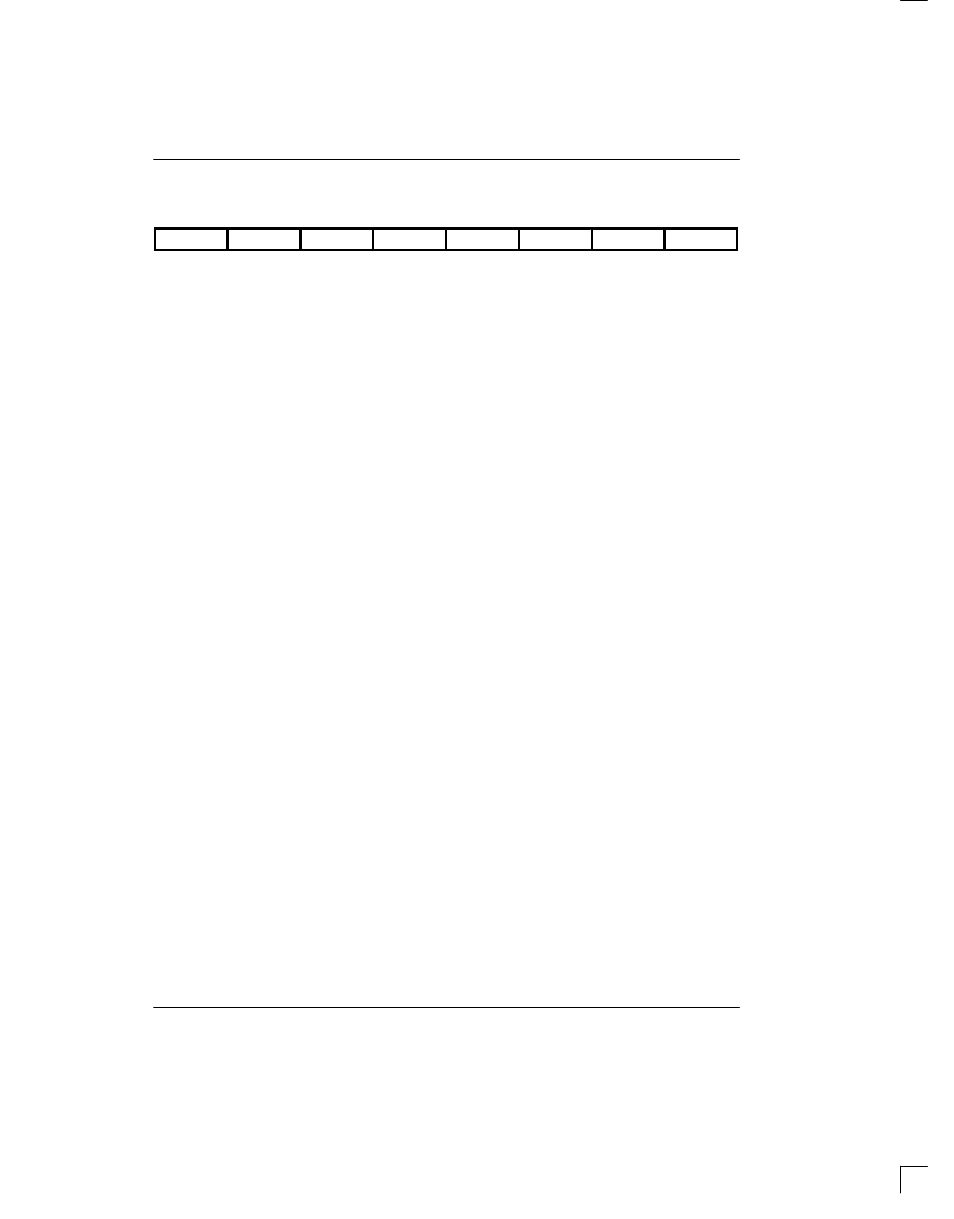

RSR: RECEIVE STATUS REGISTER Figure 17

(MSB)

(LSB)

BVCS

ECS

RYEL

RCL

FERR

B8ZSD

RBL

RLOS

SYMBOL

POSITION

NAME AND DESCRIPTION

BVCS

RSR.7

Bipolar Violation Count Saturation. Set when the 8-bit counter at BVCR

saturates.

ECS

RSR.6

Error Count Saturation. Set when either of the 4-bit counters at ECR satu-

rates.

RYEL

RSR.5

Receive Yellow Alarm. Set when yellow alarm detected. (Detected yellow

alarm format determined by CCR.4 and CCR.3.)

RCL

RSR.4

Receive Carrier Loss. Set when 32 consecutive 0’s appear at RPOS and

RNEG.

FERR

RSR.3

Frame Bit Error. Set when F

T

(193S) or FPS (193E) bit error occurs.

B8ZSD

RSR.2

Bipolar Eight Zero Substitution Detect. Set when B8ZS code word de-

tected.

RBL

RSR.1

Receive Blue Alarm. Set when two consecutive frames have less than

three 0’s (total) in the data stream (F-bit positions not tested).

RLOS

RSR.0

Receive Loss of Sync. Set when resync is in process; if RCR.1=0, RLOS

transitions high on an OOF event or carrier loss indicating auto resync.

RECEIVE ALARM REPORTING

Incoming serial data is monitored by the transceiver for

alarm occurrences. Alarm conditions are reported in

two ways: via transitions on the alarm output pins and

registered interrupt, in which the host controller reads

the RSR in response to an alarm-driven interrupt. Inter-

rupts may be direct, in which the transceiver demands

service for a real-time alarm, or count-overflow trig-

gered, in which an onboard alarm event counter ex-

ceeds a user-programmed threshold. The user may

mask individual alarm conditions by clearing the ap-

propriate bits in the receive interrupt mask register

(RIMR).

ALARM SERVICING

The host controller must service the transceiver in order

to clear an interrupt condition. Clearing appropriate bits

in the RIMR will unconditionally clear an interrupt. Direct

interrupt (those driven from real-time alarms) will be

cleared when the RSR is directly read unless the alarm

condition still exists. Count-overflow interrupts (BVCS,

ECS) are not cleared by a direct read of the RSR. They

will be cleared only when the user presets the appropri-

ate count register to a value other than all 1’s. A burst

read of the RSR will not clear an interrupt condition.