Rainbow Electronics DS2180A User Manual

Page 19

DS2180A

041995 19/36

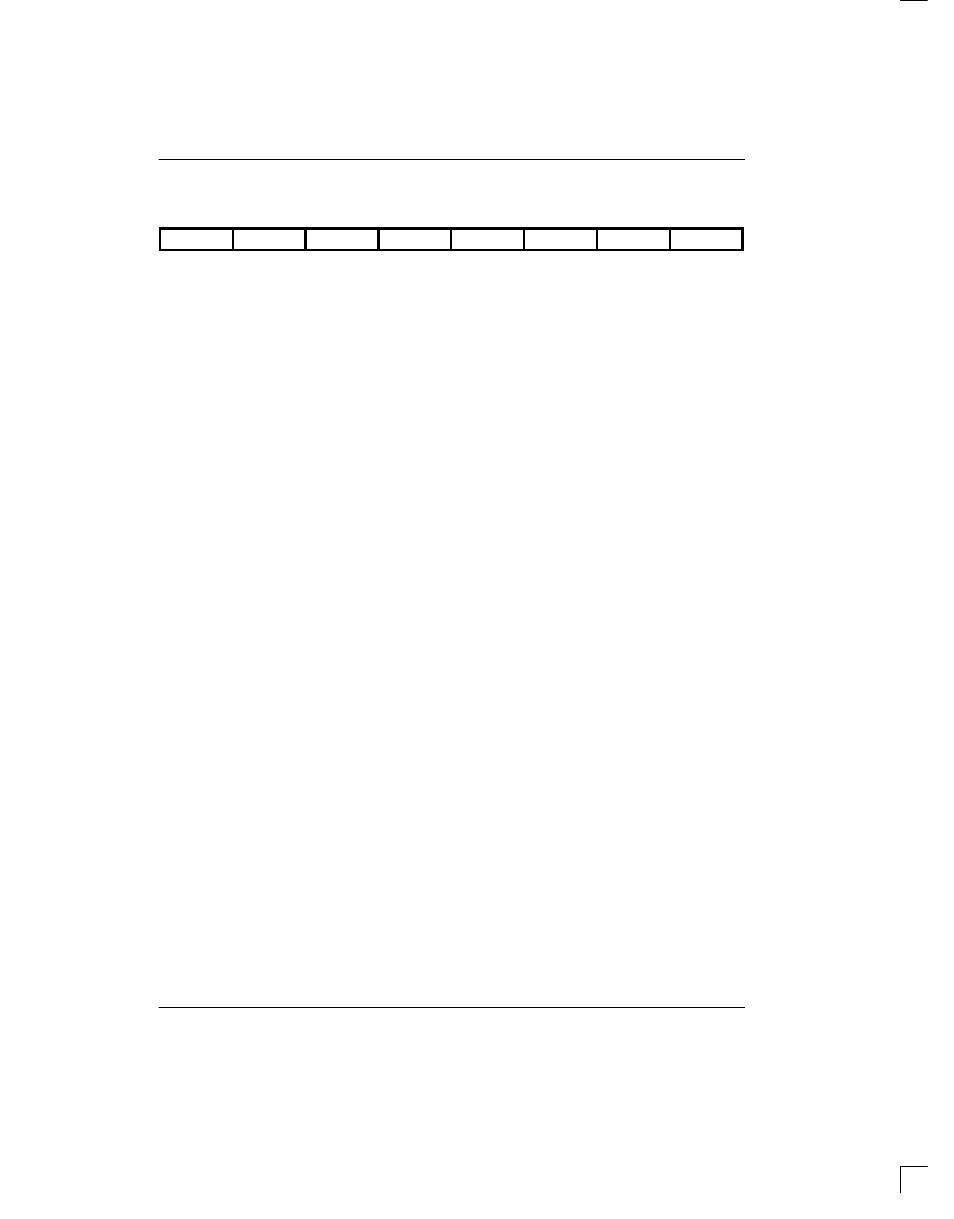

RIMR: RECEIVE INTERRUPT MASK REGISTER Figure 18

(MSB)

(LSB)

BVCS

ECS

RYEL

RCL

FERR

B8ZSD

RBL

RLOS

SYMBOL

POSITION

NAME AND DESCRIPTION

BVCS

RIMR.7

Bipolar Violation Count Saturation Mask.

1 = Interrupt masked.

0 = Interrupt masked.

ECS

RIMR.6

Error Count Saturation Mask.

1 = Interrupt enabled.

0 = Interrupt masked.

RYEL

RIMR.5

Receive Yellow Alarm Mask.

1 = Interrupt enabled.

0 = Interrupt masked.

RCL

RIMR.4

Receive Carrier Loss Mask.

1 = Interrupt enabled.

0 = Interrupt masked.

FERR

RIMR.3

Frame Bit Error Mask.

1 = Interrupt enabled.

0 = Interrupt masked.

B8ZSD

RIMR.2

B8ZS Detect Mask.

1 = Interrupt enabled.

0 = Interrupt masked.

RBL

RIMR.1

Receive Blue Alarm Mask.

1 = Interrupt enabled.

0 = Interrupt masked.

RLOS

RIMR.0

Receive Loss of Sync Mask.

1 = Interrupt enabled.

0 = Interrupt masked.

ALARM COUNTERS

The three onboard alarm event counters allow the trans-

ceiver to monitor and record error events without pro-

cessor intervention on each event occurrence. All of

these counters are presettable by the user establishing

an event count interrupt threshold. As each counter sat-

urates, the next error event occurrence will set a bit in

the RSR and generate an interrupt unless masked. The

user may read these registers at any time; in many sys-

tems, the host will periodically poll these registers to es-

tablish link error rate performance.

OOF EVENTS AND ERRORED

SUPERFRAMES

Out of frame is declared when at least two of four (or

five) consecutive framing bits are in error. F

T

bits are

tested for OOF occurrence in 193S; the FPS bits are

tested in 193E. OOF events are recorded by the 4-bit

OOF counter in the error counter register. In the 193E

framing mode, the OOF event is logically OR’ed with an

on-chip generated CRC checksum. This event, known

as errored superframe, is recorded by the 4-bit ESF er-

ror counter in the error count register. In the 193S fram-

ing mode, the 4-bit ESF error counter records individual

F

T

and F

S

errors when RCR.3=1 or F

T

errors only when

RCR.3=0.