Rainbow Electronics DS2180A User Manual

Page 14

DS2180A

041995 14/36

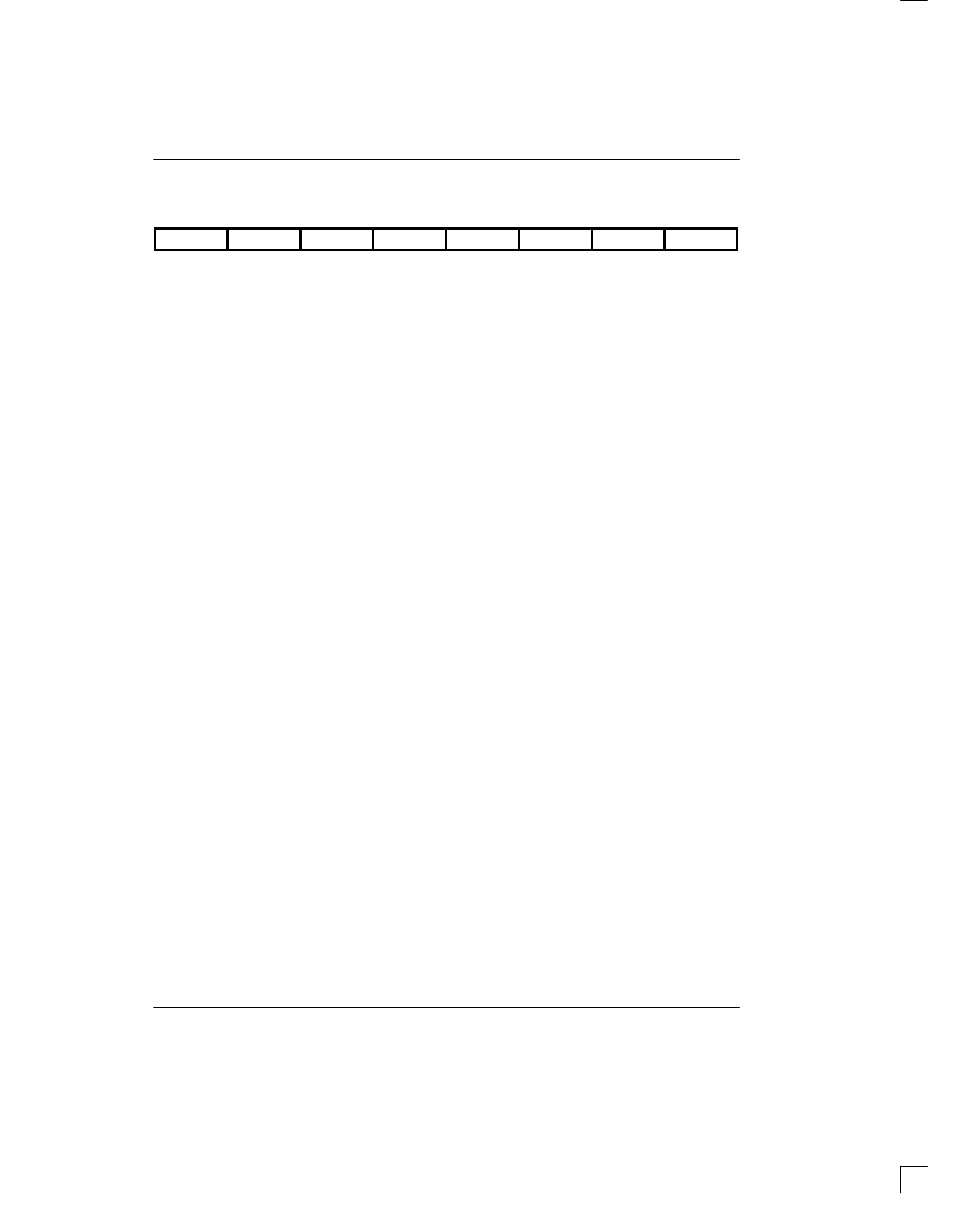

RECEIVE CONTROL REGISTER Figure 12

(MSB)

(LSB)

ARC

OOF

RCI

RCS

SYNCC

SYNCT

SYNCE

RESYNC

SYMBOL

POSITION

NAME AND DESCRIPTION

ARC

RCR.7

Auto Resync Criteria.

0 = Resync on OOF or RCL event.

1 = Resync on OOF only.

OOF

RCR.6

Out-of-frame (OOF) Condition Detection.

0 = 2 of 4 framing bits in error.

1 = 2 of 5 framing bits in error.

RCI

RCR.5

Receive Code Insert. When set, the receive code selected by RCR.4 is

inserted into channels marked by RMR registers. If clear, no code is in-

serted.

RCS

RCR.4

Receive Code Select.

0 = Idle code (7F Hex).

1 = Digital milliwatt.

SYNCC

RCR.3

Sync Criteria. Determines the type of algorithm utilized by the receive syn-

chronizer and differs for each frame mode.

193S Framing (CCR.4=0).

0 = Synchronize to frame boundaries using F

T

pattern, then search for mul-

tiframe by using F

S

.

1 = Cross couple F

T

and F

S

patterns in sync algorithm.

193E Framing (CCR.4=1).

0 = Normal sync (utilizes FPS only).

1 = Validate new alignment with CRC before declaring sync.

SYNCT

RCR.2

Sync Time. If set, 24 consecutive F-bits of the framing pattern must be

qualified before sync is declared. If clear, 10 bits are qualified.

SYNCE

RCR.1

Sync Enable. If clear, the transceiver will automatically begin a resync if

two of the previous four or five framing bits were in error or if carrier loss is

detected. If set, no auto resync occurs.

RESYNC

RCR.0

Resync. When toggled low to high, the transceiver will initiate resync im-

mediately. The bit must be cleared, then set again for subsequent resyncs.

RECEIVE CODE INSERTION

Incoming receive channels can be replaced with idle (7F

Hex) or digital milliwatt (

µ

-LAW format) codes. The re-

ceive mark registers indicate which channels are in-

serted. When set, bit RCR.5 serves as a “global” enable

for marked channels and bit RCR.4 selects inserted

code format: 0 = idle code, 1 = digital milliwatt.

RECEIVE SYNCHRONIZER

Bits RCR.0 through RCR.3 allow the user to control op-

erational characteristics of the synchronizer. Sync algo-

rithm, candidate qualify testing, auto resync, and com-

mand resync modes may be altered at any time in

response to changing span conditions.