Rainbow Electronics W79E8213R User Manual

Page 67

Preliminary W79E8213/W79E8213R Data Sheet

Publication Release Date: July 11, 2008

- 67 -

Revision A2

any errant code is executed now, then the reset Watchdog Timer instructions will not be executed at

the required instants and Watchdog reset will occur.

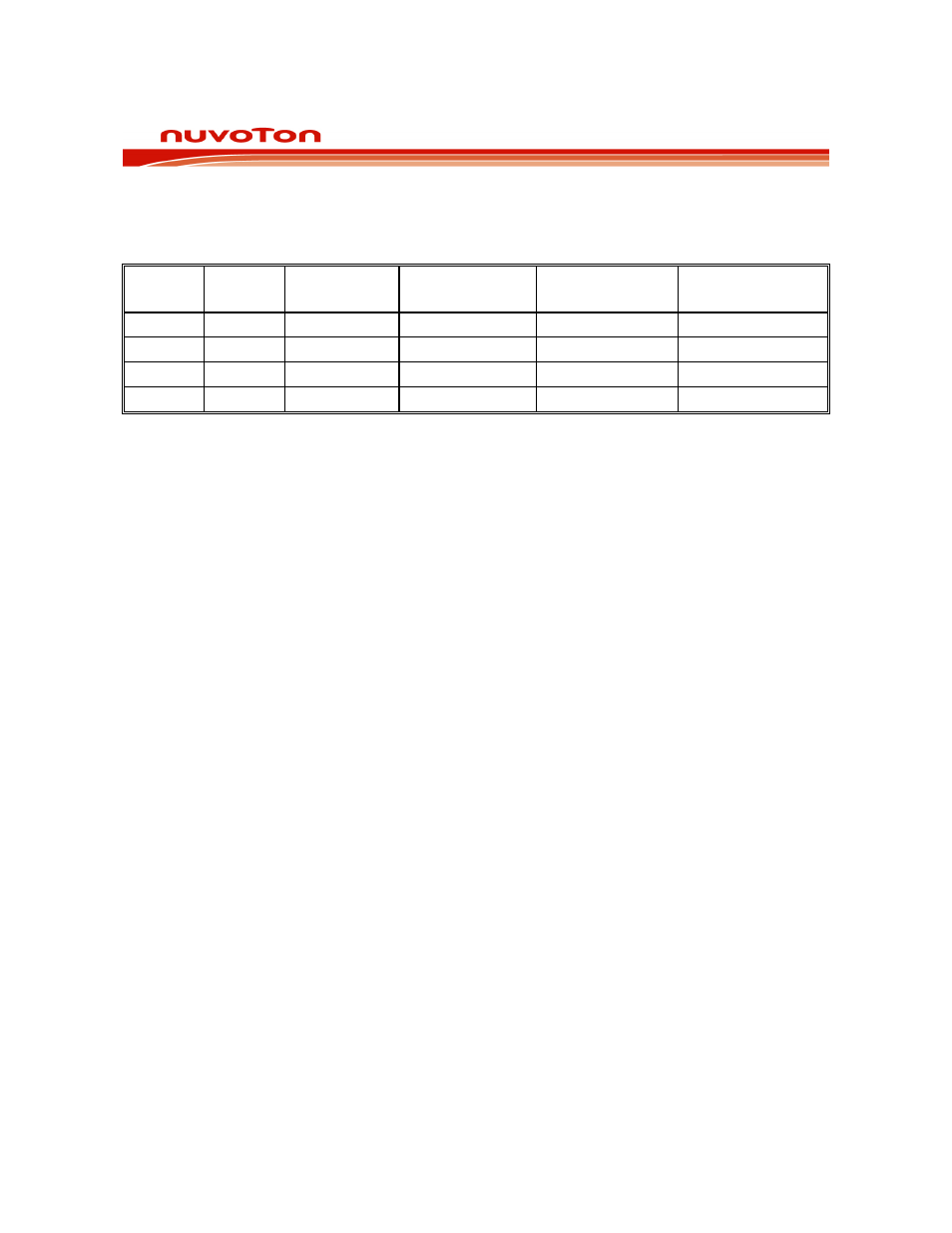

The Watchdog Timer time-out selection will result in different time-out values depending on the clock

speed. The reset, when enabled, will occur when 512 clocks after time-out has occurred.

WD1 WD0

INTERRUPT

TIME-OUT

RESET

TIME-OUT

NUMBER OF

CLOCKS

TIME

@ 10 MHZ

0 0 2

17

2

17

+ 512

131072

13.11 mS

0 1 2

20

2

20

+ 512

1048576

104.86 mS

1 0 2

23

2

23

+ 512

8388608

838.86 mS

1 1 2

26

2

26

+ 512

67108864

6710.89 mS

Table 15-1: Time-out values for the Watchdog Timer

The Watchdog Timer will be disabled by a power-on/fail reset. The Watchdog Timer reset does not

disable the Watchdog Timer, but will restart it. In general, software should restart the timer to put it into

a known state. The control bits that support the Watchdog Timer are discussed below.

15.1 WATCHDOG CONTROL

WDIF: WDCON.3 - Watchdog Timer Interrupt flag. This bit is set whenever the time-out occurs in the

Watchdog Timer. If the Watchdog interrupt is enabled (EIE.4), then an interrupt will occur (if the global

interrupt enable is set and other interrupt requirements are met). Software or any reset can clear this

bit.

WTRF: WDCON.2 - Watchdog Timer Reset flag. This bit is set whenever a watchdog reset occurs.

This bit is useful for determined the cause of a reset. Software must read it, and clear it manually. A

Power-fail reset will clear this bit. If EWRST = 0, then this bit will not be affected by the Watchdog

Timer.

EWRST: WDCON.1 - Enable Watchdog Timer Reset. This bit when set to 1 will enable the Watchdog

Timer reset function. Setting this bit to 0 will disable the Watchdog Timer reset function, but will leave

the timer running.

WDCLR: WDCON.0 - Reset Watchdog Timer. This bit is used to clear the Watchdog Timer and to

restart it. This bit is self-clearing, so after the software writes 1 to it the hardware will automatically

clear it. If the Watchdog Timer reset is enabled, then the WDCLR has to be set by the user within 512

clocks of the time-out. If this is not done then a Watchdog Timer reset will occur.

15.2 CLOCK CONTROL of Watchdog

WD1, WD0: WDCON.5, WDCON.4 - Watchdog Timer Mode select bits. These two bits select the

time-out interval for the watchdog timer. The reset time is 512 clocks longer than the interrupt time-out

value.

The default Watchdog time-out is 2

17

clocks, which is the shortest time-out period. The WDRUN, WD0,

WD1, EWRST, WDIF and WDCLR bits are protected by the Timed Access procedure. This prevents

software from accidentally enabling or disabling the watchdog timer. More importantly, it makes it

highly improbable that errant code can enable or disable the Watchdog Timer.