Rainbow Electronics W79E8213R User Manual

Page 26

Preliminary W79E8213/W79E8213R Data Sheet

Publication Release Date: July 11, 2008

- 26 -

Revision A2

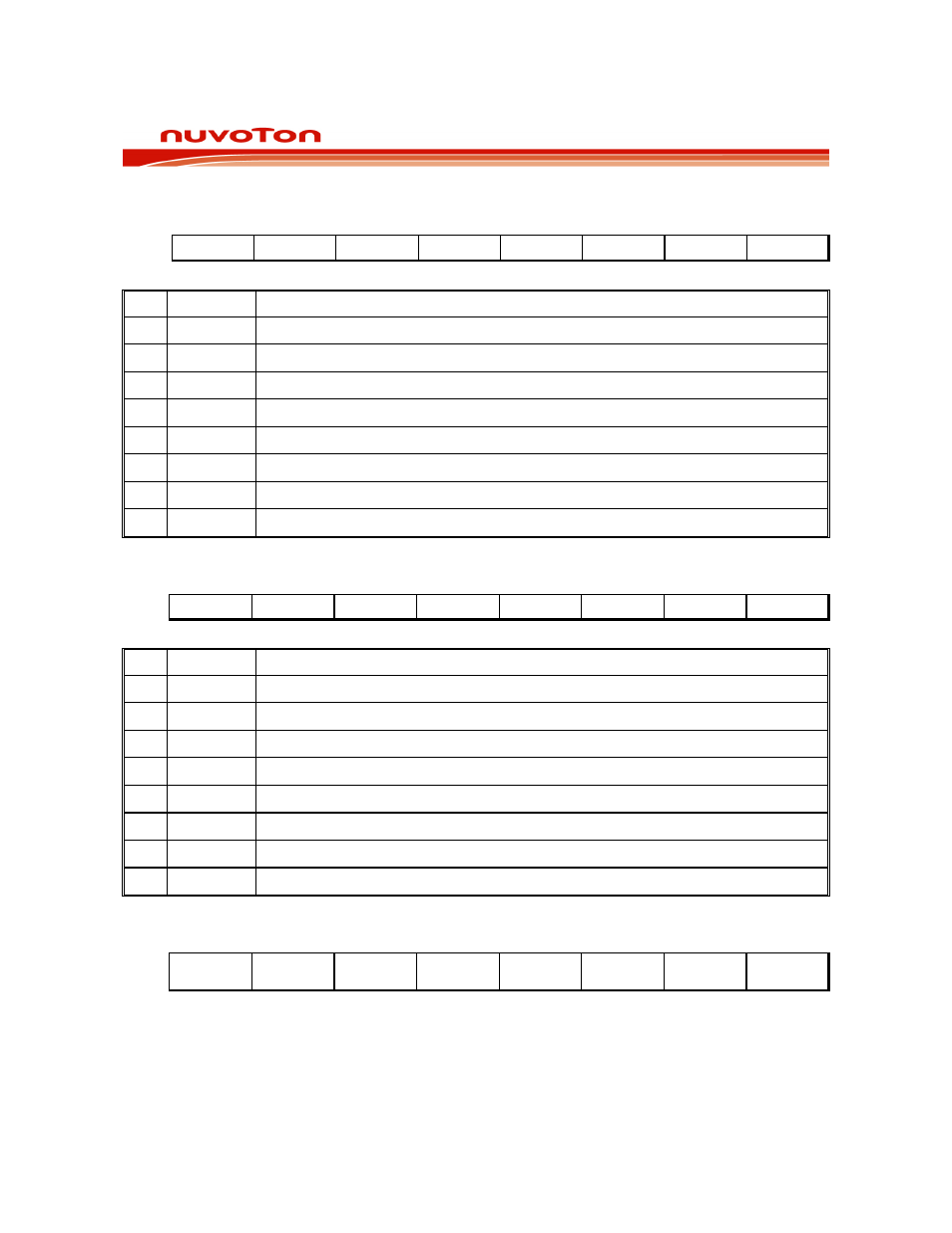

INTERRUPT HIGH PRIORITY

Bit:

7 6 5 4 3 2 1 0

-

PADCH

PBOH -

PT1H PX1H PT0H PX0H

Mnemonic: IP0H

Address: B7h

BIT NAME

FUNCTION

7

-

This bit is un-implemented and will read high.

6

PADCH

1: To set interrupt high priority of ADC is highest priority level.

5

PBOH

1: To set interrupt high priority of Brown Out Detector is highest priority level.

4 -

Reserved.

3

PT1H

1: To set interrupt high priority of Timer 1 is highest priority level.

2

PX1H

1: To set interrupt high priority of External interrupt 1 is highest priority level.

1

PT0H

1: To set interrupt high priority of Timer 0 is highest priority level.

0

PX0H

1: To set interrupt high priority of External interrupt 0 is highest priority level.

INTERRUPT PRIORITY 0

Bit:

7 6 5 4 3 2 1 0

- PADC

PBO

- PT1

PX1

PT0

PX0

Mnemonic: IP

Address: B8h

BIT NAME

FUNCTION

7

-

This bit is un-implemented and will read high.

6

PADC

1: To set interrupt priority of ADC is higher priority level.

5

PBO

1: To set interrupt priority of Brown Out Detector is higher priority level.

4 -

Reserved.

3

PT1

1: To set interrupt priority of Timer 1 is higher priority level.

2

PX1

1: To set interrupt priority of External interrupt 1 is higher priority level.

1

PT0

1: To set interrupt priority of Timer 0 is higher priority level.

0

PX0

1: To set interrupt priority of External interrupt 0 is higher priority level.

NVM LOW BYTE ADDRESS

Bit:

7 6 5 4 3 2 1 0

-

NVMADDR

.6

NVMADDR

.5

NVMADDR

.4

NVMADDR

.3

NVMADDR

.2

NVMADDR

.1

NVMADDR

.0

Mnemonic: NVMADDRL

Address: C6h