Rainbow Electronics W79E8213R User Manual

Page 31

Preliminary W79E8213/W79E8213R Data Sheet

Publication Release Date: July 11, 2008

- 31 -

Revision A2

Continued

BIT NAME

FUNCTION

2 WTRF

Watchdog Timer Reset Flag

1: Hardware will set this bit when the watchdog timer causes a reset. Software

can read it but must clear it manually. A power-fail reset will also clear the

bit. This bit helps software in determining the cause of a reset. If EWRST =

0, the watchdog timer will have no affect on this bit.

1 EWRST

0: Disable Watchdog Timer Reset.

1: Enable Watchdog Timer Reset.

0 WDCLR

Reset Watchdog Timer

This bit helps in putting the watchdog timer into a know state. It also helps in

resetting the watchdog timer before a time-out occurs. Failing to set the

EWRST before time-out will cause an interrupt, if EWDI (EIE.4) is set, and 512

clocks after that a watchdog timer reset will be generated if EWRST is set. This

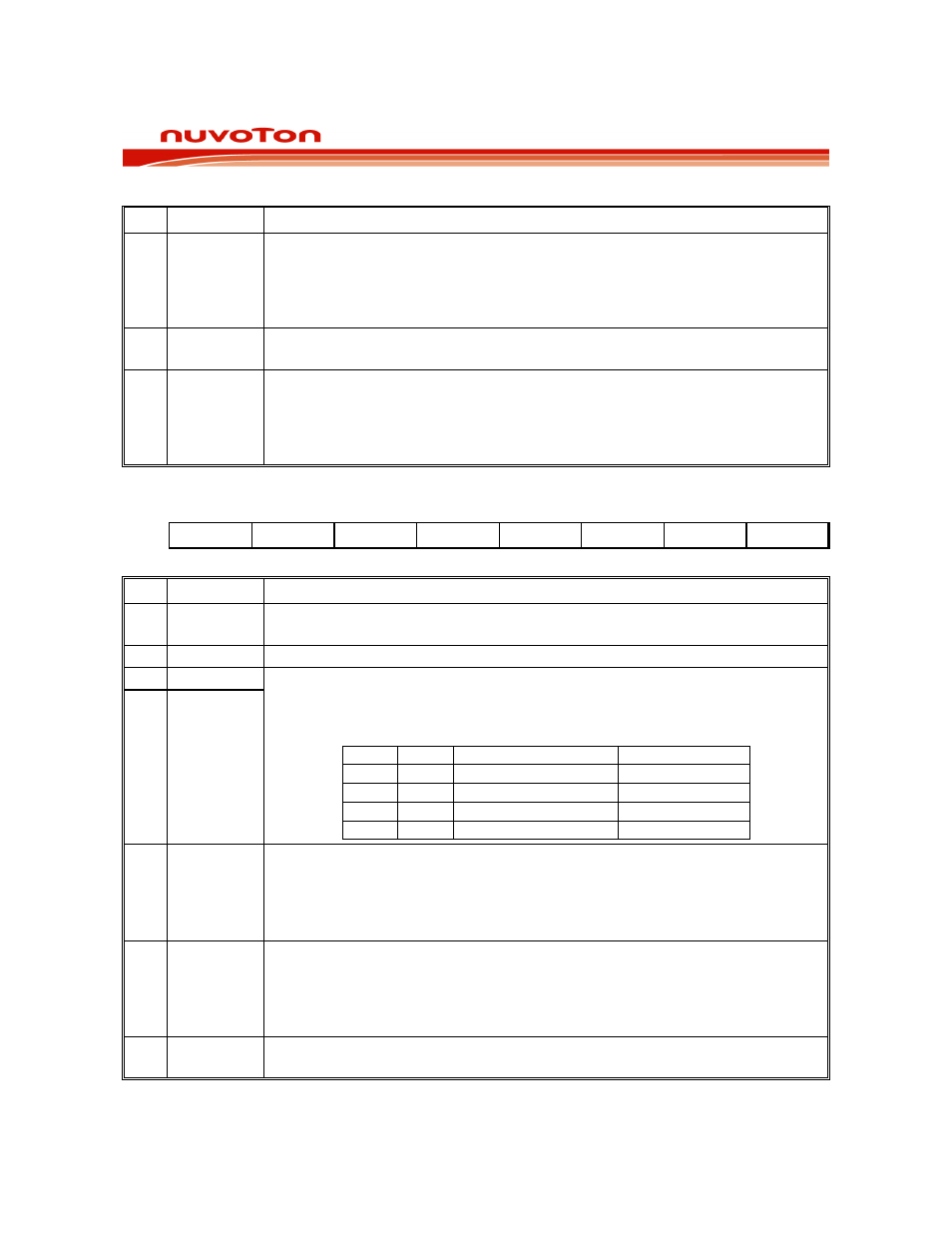

WATCHDOG CONTROL

Bit:

7 6 5 4 3 2 1 0

WDRUN

-

WD1 WD0 WDIF WTRF

EWRST

WDCLR

Mnemonic: WDCON

Address: D8h

BIT NAME

FUNCTION

7 WDRUN

0: The Watchdog is stopped.

1: The Watchdog is running.

6 -

Reserved.

5 WD1

4 WD0

Watchdog Timer Time-out Select bits. These bits determine the time-out period

of the watchdog timer. The reset time-out period is 512 clocks longer than the

watchdog time-out.

WD1

WD0

Interrupt time-out

Reset time-out

0 0

2

17

2

17

+ 512

0 1

2

20

2

20

+ 512

1 0

2

23

2

23

+ 512

1 1

2

26

2

26

+ 512

3 WDIF

Watchdog Timer Interrupt Flag

0: If the interrupt is not enabled, then this bit indicates that the time-out period

has elapsed. This bit must be cleared by software.

1: If the watchdog interrupt is enabled, hardware will set this bit to indicate that

the watchdog interrupt has occurred.

2 WTRF

Watchdog Timer Reset Flag

1: Hardware will set this bit when the watchdog timer causes a reset. Software

can read it but must clear it manually. A power-fail reset will also clear the

bit. This bit helps software in determining the cause of a reset. If EWRST =

0, the watchdog timer will have no affect on this bit.

1 EWRST

0: Disable Watchdog Timer Reset.

1: Enable Watchdog Timer Reset.