Power-management mode, Switchback, Table 6. maxq3108 clock divisors – Rainbow Electronics MAXQ3108 User Manual

Page 53: Maxq3108 low-power, dual-core microcontroller

MAXQ3108

Low-Power, Dual-Core Microcontroller

______________________________________________________________________________________

53

modes. The two power-management modes reduce

speed and power consumption by either internally

dividing the clock signal by 256 or using the 32kHz

clock directly. The stop mode stops all internal clocks

(with the exception of the 32kHz crystal amplifier)

resulting in a static condition and providing the lowest

power state.

The power supervisor monitors the V

DD

level when

power is first applied to the device and generates a

power-on reset when the voltage reaches an accept-

able level, and following the 65,536 FLL cycle power-up

period.

The power-on reset initializes the processor and allows

program execution at the reset vector location of

8000h. The power-on reset flag, POR, is set to logic 1 to

indicate a power-on reset has occurred; the POR flag

can only be cleared by software.

Power-Management Mode

Power-management mode (PMM) allows application

software to dynamically match operating frequency with

the need for lower operating power when full process-

ing throughput is not required. When power-manage-

ment mode 1 (PMM1) is used, the system clock is

divided by 256, resulting in a user core clock rate of

19.584kHz. When power-management mode 2 (PMM2)

is used, the system clock is driven directly by the

32,768Hz clock source resulting in a user core clock of

16.384kHz.

PMM reduces operating power by minimizing power

loss due to CMOS switching transients. PMM is invoked

by setting the PMM enable bit (PMME). The PMME bit

defaults to 0 on all forms of reset.

When the system is operated in PMM2 mode, the high-

frequency clock is disabled unless the switchback is

active or the DSPCore is enabled. Refer to the PMME

bit description in the

MAXQ Family User’s Guide

for

more information.

Switchback

The switchback feature allows low-power operation

associated with PMM, but maintains quick response to

events that require full processing capacity. The switch-

back function is enabled by setting the SWB bit to logic

1. When operating in a PMM mode and the SWB bit is

enabled, the system restores the clock settings that

were active when PMM was invoked whenever the sys-

tem detects a qualified event.

The automatic switchback is only enabled when PMM is

in use. Switchback to the high-frequency clock occurs

whenever any of these conditions occur:

• Detection of a selected edge transition on any of the

external interrupts when the respective pin has inter-

rupts enabled.

• UART activity:

• When the serial port is enabled to receive data and

a transition occurs on the receive input pin (for

mode 1, 2, and 3).

• After a write access to the SBUF register.

• SPI activity:

• SPIB is written in master mode (STBY = 1).

• The SSEL signal is asserted in slave mode.

• Time-of-day alarm or subsecond alarm from the RTC

when enabled.

• I

2

C activity:

• Start interrupt when enabled (I2CSRIE = 1).

• A write to the I2CSTART bit when the I

2

C controller

is in master mode (I2CMST = 1).

• SVM interrupt if enabled (SVMIE = 1).

• Changing the value of ADCONV from 0 to 1.

• Active debug mode is entered either by breakpoint

match or issuance of the debug command from

background mode.

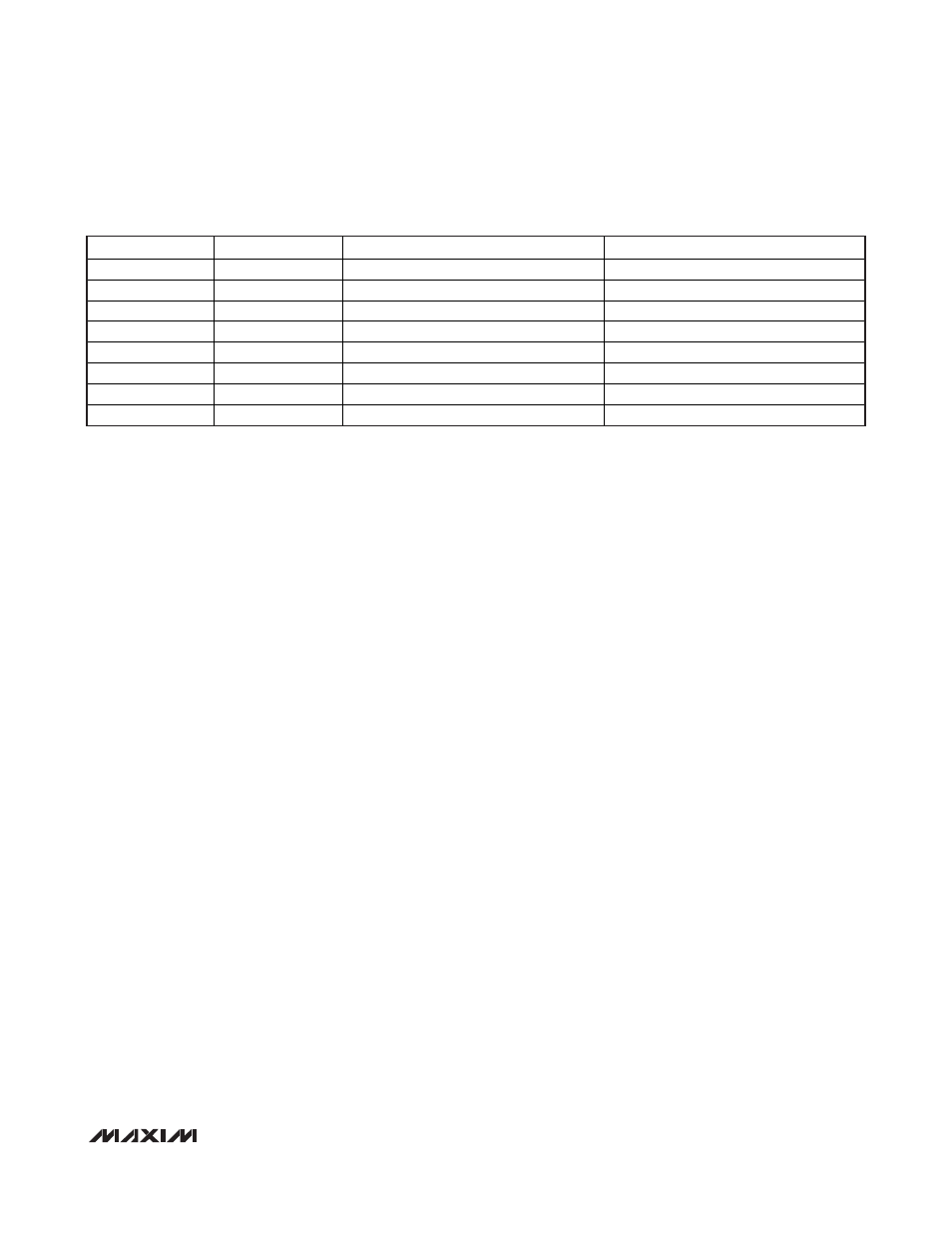

PMME

CD[1:0]

DIVIDE RATIO

CLOCK SOURCE

0 00

1

(default)

FLLSL

0 01

2

FLLSL

0 10

4

FLLSL

0 11

8

FLLSL

1 00

256

FLLSL

1 01

Reserved

(256)

FLLSL

1 10

Reserved

(256)

FLLSL

1 11

1

CX1

Table 6. MAXQ3108 Clock Divisors