Maxq3108 low-power, dual-core microcontroller – Rainbow Electronics MAXQ3108 User Manual

Page 38

MAXQ3108

Low-Power, Dual-Core Microcontroller

38

______________________________________________________________________________________

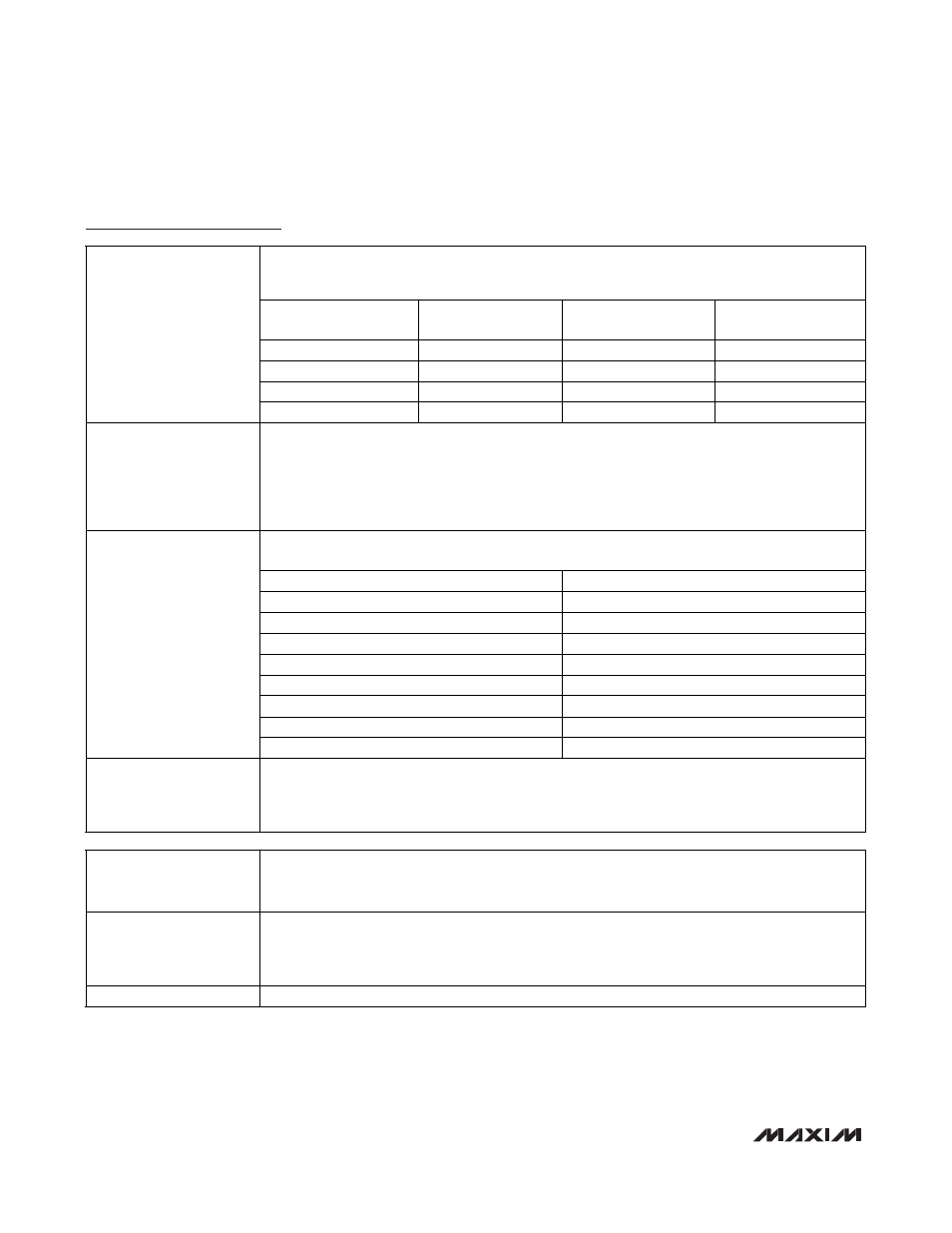

Special Function Register Bit Descriptions (continued)

Timer 2 Capture/Compare Function Select. These bits, in conjunction with the C/T2 bit, select the

basic operating mode of timer 2. In the dual 8-bit mode of operation (T2MD = 1), the secondary

timer (T2L) always operates in compare mode.

CCF[1:0] EDGE(S)

C/T2 = 0 (TIMER

MODE)

C/T2 = 1 (COUNTER

MODE)

00 None

Compare

Mode

Disabled

01 Rising

Capture/Reload

Counter

10 Falling

Capture/Reload

Counter

T2CFG.[2:1]: CCF[1:0]

11

Rising and Falling

Capture/Reload

Counter

T2CFG.3: T2MD

Timer 2 Mode Select. This bit enables the dual 8-bit mode of operation. The default reset state is

0, which selects the 16-bit mode of operation. When the dual 8-bit mode is established, the primary

timer/counter (T2H) carries all the counter/capture functionality with it while the secondary 8- bit

timer (T2L) must operate in timer compare mode, sourcing the defined internal clock.

0: 16-bit mode (default)

1: dual 8-bit mode

Timer 2 Clock Divide 2:0 Bits. These three bits select the divide ratio for the timer clock when

operating in timer mode.

T2DIV[2:0] DIVIDE

RATIO

000 1

001 2

010 4

011 8

100 16

101 32

110 64

T2CFG.[6:4]: T2DIV[2:0]

111 128

T2CFG.7: T2CI

Timer 2 Clock Input Select Bit. Setting this bit enables an alternate input clock source to the timer

2 block. The alternate input clock selection is the 32kHz clock. The alternate input clock must be

sampled by the system clock, which requires that the system clock be at least 4 x 32kHz for

proper operation.

MCNT (00h, 03h)

Multiplier Control Register

Initialization:

This register is cleared to 0000h on all forms of reset.

Read/Write Access:

Unrestricted read, write is allowed for all bits except bit 7 and 15. Bit 7 and 15 are read-only.

MCNT.0: SUS

Signed-Unsigned. This bit determines the data type of the operands. When this bit is cleared to 0,

the multiplier performs a signed operation; the operands are two’s complement values. When this

bit is set to logic 1, the multiplier performs an unsigned operation with the operands as absolute

magnitudes.

MCNT.1: MMAC

Multiply-Accumulate Enable