Maxq3108 low-power, dual-core microcontroller – Rainbow Electronics MAXQ3108 User Manual

Page 44

MAXQ3108

Low-Power, Dual-Core Microcontroller

44

______________________________________________________________________________________

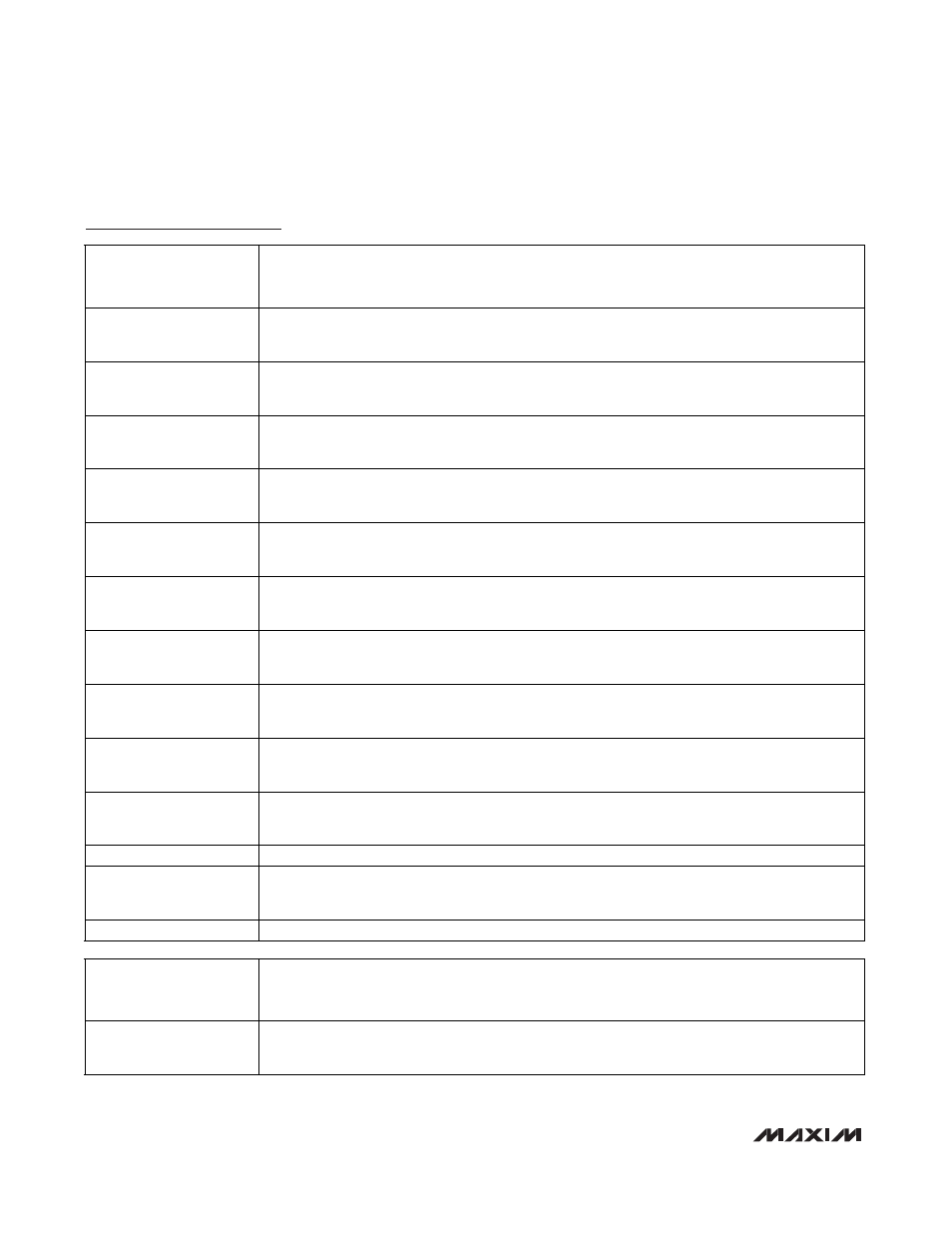

Special Function Register Bit Descriptions (continued)

I2CIE (02h, 04h)

I

2

C Interrupt Enable Register (16-Bit Register)

Initialization:

This register is cleared to 0000h on all forms of reset.

Read/Write Access: Unrestricted

read/write

access.

I2CIE.0: I2CSRIE

I

2

C START Interrupt Enable. Setting this bit to 1 causes an interrupt to the CPU when a START

condition is detected (I2CSRI = 1). Clearing this bit to 0 disables the START detection interrupt

from generating.

I2CIE.1: I2CTXIE

I

2

C Transmit Complete Interrupt Enable. Setting this bit to 1 causes an interrupt to the CPU when

the transmit interrupt flag is set (I2CTXI = 1). Clearing this bit to 0 disables the transmit interrupt

from generating.

I2CIE.2: I2CRXIE

I

2

C Receive Ready Interrupt Enable. Setting this bit to 1 causes an interrupt to the CPU when the

receive interrupt flag is set (I2CRXI = 1). Clearing this bit to 0 disables the receive interrupt from

generating.

I2CIE.3: I2CSTRIE

I

2

C Clock Stretch Interrupt Enable. Setting this bit to 1 generates an interrupt to the CPU when the

clock stretch interrupt flag is set (I2CSTRI = 1). Clearing this bit disables the clock stretch interrupt

from generating.

I2CIE.4: I2CTOIE

I

2

C Timeout Interrupt Enable. Setting this bit to 1 causes an interrupt to the CPU when a timeout

condition is detected (I2CTOI = 1). Clearing this bit to 0 disables the timeout interrupt from

generating.

I2CIE.5: I2CAMIE

I

2

C Slave Address Match Interrupt Enable. Setting this bit to 1 causes an interrupt to the CPU

when the I

2

C controller detects an address that matches the I2CSLA value (I2CAMI = 1). Clearing

this bit to 0 disables the address match interrupt from generating.

I2CIE.6: I2CALIE

I

2

C Arbitration Loss Enable. Setting this bit to 1 causes an interrupt to the CPU when the I

2

C

master loses in an arbitration (I2CALI = 1). Clearing this bit to 0 disables the arbitration loss

interrupt from generating.

I2CIE.7: I2CNACKIE

I

2

C NACK Interrupt Enable. Setting this bit to 1 causes an interrupt to the CPU when a NACK is

detected (I2CNACKI = 1). Clearing this bit to 0 disables the NACK detection interrupt from

generating.

I2CIE.8: I2CGCIE

I

2

C General Call Interrupt Enable. Setting this bit to 1 generates an I2CGCI (general call interrupt)

to the CPU when general call is enabled (I2CGCEN = 1). Clearing this bit to 0 disables the general

call interrupt from generating.

I2CIE.9: I2CROIE

I

2

C Receiver Overrun Interrupt Enable. Setting this bit to 1 causes an interrupt to the CPU when a

receiver overrun condition is detected (I2ROI = 1). Clearing this bit to 0 disables the receiver

overrun detection interrupt from generating.

I2CIE.10: Reserved

Reserved. Reads return 0.

I2CIE.11: I2CSPIE

I

2

C STOP Interrupt Enable. Setting this bit to 1 causes an interrupt to the CPU when a STOP

condition is detected (I2CSPI = 1). Clearing this bit to 0 disables the STOP detection interrupt from

generating.

I2CIE.[15:12]: Reserved

Reserved. Reads return 0.

TB0R (04h, 04h)

Timer B 0 Capture/Reload Value

Initialization:

This register is cleared to 0000h on all forms of reset.

Read/Write Access:

Unrestricted read/write.

TB0R.[15:0]:

Timer B Capture/Reload Bits 15:0. This register is used to capture the TBV value when timer B is

configured in capture mode. This register is also used as the 16-bit reload value when timer B is

configured in autoreload mode.