Maxq3108 low-power, dual-core microcontroller – Rainbow Electronics MAXQ3108 User Manual

Page 30

MAXQ3108

Low-Power, Dual-Core Microcontroller

30

______________________________________________________________________________________

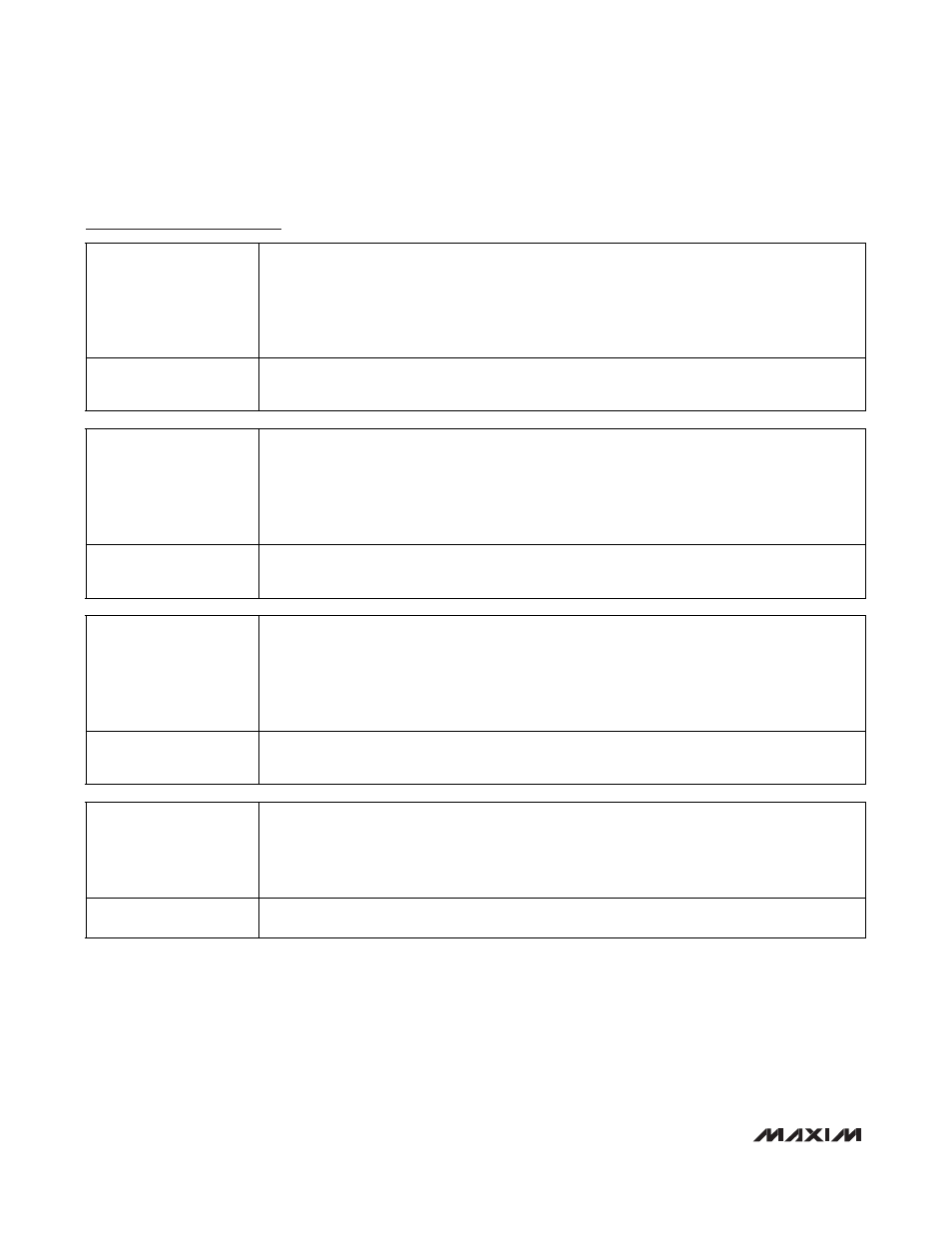

Special Function Register Bit Descriptions (continued)

RTSS (1Ah, 01h)

RTC Subsecond Counter Register (8-Bit Register)

Initialization:

This register is battery backed through POR so long as V

BAT(MIN)

< V

BAT

< V

BAT(MAX)

; however, it

is indeterminate on the very first POR and must be configured initially by the user. This register is

unaffected by other resets.

Read/Write Access:

Write accessible when RTCE = 0 and BUSY = 0. Read accessible at all times, but the value could

be indeterminate if RDY = 0. Software should be careful to read this register only when RDY = 1.

RTSS.[7:0]:

RTC Subsecond Counter Bit 7:0. This ripple counter represents 1/256-second resolution for the

RTC and its content is incremented with each 256Hz clock tick derived from the 32.768kHz

oscillator. When the counter rollover, its output is used to drive the 32-bit second counter.

RTSH (1Bh, 01h)

RTC Second Counter High Register (16-Bit Register)

Initialization:

This register is battery backed through POR so long as V

BAT(MIN)

< V

BAT

< V

BAT(MAX)

; however, it

is indeterminate on the very first POR and must be configured initially by the user. This register is

unaffected by other resets.

Read/Write Access:

Write accessible when RTCE = 0 and BUSY = 0. Read accessible at all times, but the value could

be indeterminate if RDY = 0. Software should be careful to read this register only when RDY = 1.

RTSH.[15:0]:

RTC Second Counter High Bit 15:0. This register contains the most significant bits for the 32-bit

second counter. The RTC is a ripple counter that consists of cascading the 32-bit second counter

and 8-bit subsecond counter (RTSH, RTSL, and RTSS).

RTSL (1Ch, 01h)

RTC Second Counter Low Register (16-Bit Register)

Initialization:

This register is battery backed through POR so long as V

BAT(MIN)

< V

BAT

< V

BAT(MAX)

; however, it

is indeterminate on the very first POR and must be configured initially by the user. This register is

unaffected by other resets.

Read/Write Access:

Write accessible when RTCE = 0 and BUSY = 0. Read accessible at all times, but the value could

be indeterminate if RDY = 0. Software should be careful to read this register only when RDY = 1.

RTSL.[15:0]:

RTC Second Counter Low Bit 15:0. This register contains the least significant bits for the 32-bit

second counter. The RTC is a ripple counter that consists of cascading the 32-bit second counter

and 8-bit subsecond counter (RTSH, RTSL, and RTSS).

RSSA (1Dh, 01h)

RTC Subsecond Alarm Register (8-Bit Register)

Initialization:

This register is battery backed through POR so long as V

BAT(MIN)

< V

BAT

< V

BAT(MAX)

; however, it

is indeterminate on the very first POR and must be configured initially by the user. This register is

unaffected by other resets.

Read/Write Access:

Unrestricted read. Write accessible when BUSY = 0 and either (ASE = 0 or RTCE = 0).

RSSA.[7:0]:

RTC Subsecond Alarm Register Bit 7:0. This register contains the reload value for the subsecond

alarm. The ALSF bit is set when an autoreload occurs.