Maxq3108 low-power, dual-core microcontroller – Rainbow Electronics MAXQ3108 User Manual

Page 35

MAXQ3108

Low-Power, Dual-Core Microcontroller

______________________________________________________________________________________

35

Special Function Register Bit Descriptions (continued)

Serial Port 0 Mode Bit 0/Framing Error Flag. When FEDE is 0, this is the SM0 bit. When FEDE is

set to 1, this bit is the FE that is set upon detection of an invalid stop bit. It must be cleared by

software. Modification of this bit when FEDE is set has no effect on the serial mode.

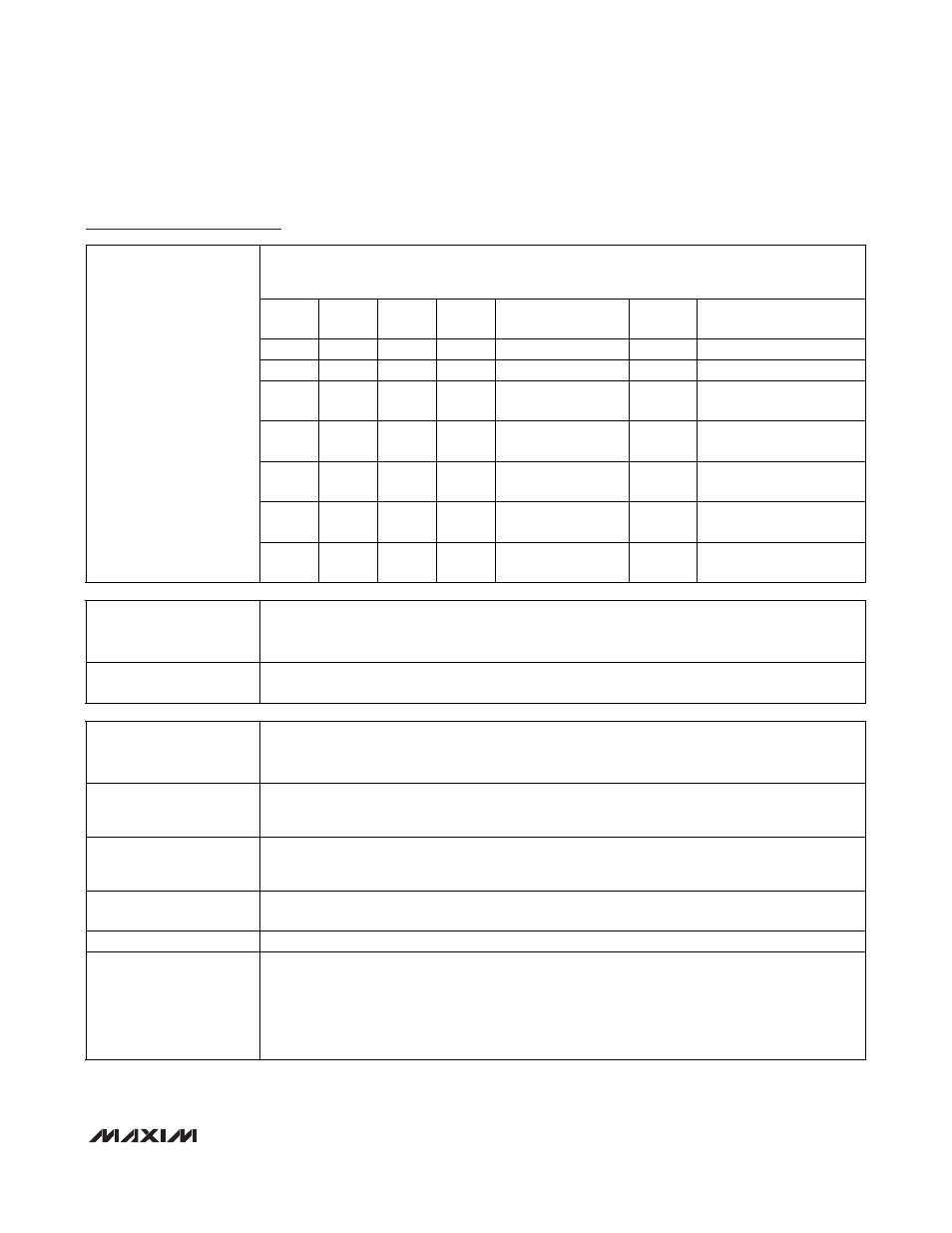

MODE SM2 SM1 SM0

FUNCTION

LENGTH

(BITS)

PERIOD

0 0 0 0

Synchronous

8

12

system

clock

0 1 0 0

Synchronous

8

4

system

clock

1 X 1 0

Asynchronous

10

64/16 baud clock

(SMOD = 0/1)

2 0 0 1

Asynchronous

11

64/32 system clock

(SMOD = 0/1)

2 1 0 1

Asynchronous

(MP)

11

64/32 system clock

(SMOD = 0/1)

3 0 1 1

Asynchronous

11

64/16 baud clock

(SMOD = 0/1)

SCON0.7:SM0/FE

3 1 1 1

Asynchronous

(MP)

11

64/16 baud clock

(SMOD = 0/1)

SBUF0 (07h, 02h)

Serial Data Buffer 0

Initialization:

This buffer is cleared to 00h on all forms of reset.

Read/Write Access: Unrestricted

read/write.

SBUF0.[7:0]:

Serial Data Buffer 0 Bit 7:0. Data for serial port 0 is read from or written to this location. The serial

transmit and receive buffers are separate, but both are addressed at this location.

SMD0 (08h, 02h)

Serial Port Mode Register 0

Initialization:

This register is cleared to 00h on all forms of reset.

Read/Write Access:

Unrestricted read/write.

SMD0.0: FEDE

Framing-Error-Detection Enable. This bit selects the function of SM0 (SCON0.7).

FEDE = 0: SCON0.7 functions as SM0 for serial-port mode selection.

FEDE = 1: SCON0.7 is converted to the FE flag.

SMD0.1: SMOD

Serial Port 0 Baud-Rate Select. The SMOD selects the final baud rate for the asynchronous mode:

SMOD = 1: 16 times the baud clock for mode 1 and 3; 32 times the system clock for mode 2.

SMOD = 0: 64 times the baud clock for mode 1 and 3; 64 times the system clock for mode 2.

SMD0.2: ESI

Enable Serial Port 0 Interrupt. Setting this bit to 1 enables interrupt requests generated by the RI

or TI flags in SCON0. Clearing this bit to 0 disables the serial port interrupt.

SMD0.[5:3]: Reserved

Reserved. Reads return 0.

SMD0.6: OFS

Output Function Select. This bit selects the PWM output function when EPWM = 1. When EPWM =

1, the OFS bit selects one of the following modes:

OFS = 0: logical NOR between UART0 TXD output and T2L waveform.

OFS = 1: logical OR between UART0 TXD output and T2L waveform.

Note that the PWM function is not possible for UART mode 0 and this bit has no effect during UART

mode 0 operation.