Maxq3108 low-power, dual-core microcontroller, Table 1. usercore peripheral registers (continued) – Rainbow Electronics MAXQ3108 User Manual

Page 11

MAXQ3108

Low-Power, Dual-Core Microcontroller

______________________________________________________________________________________

11

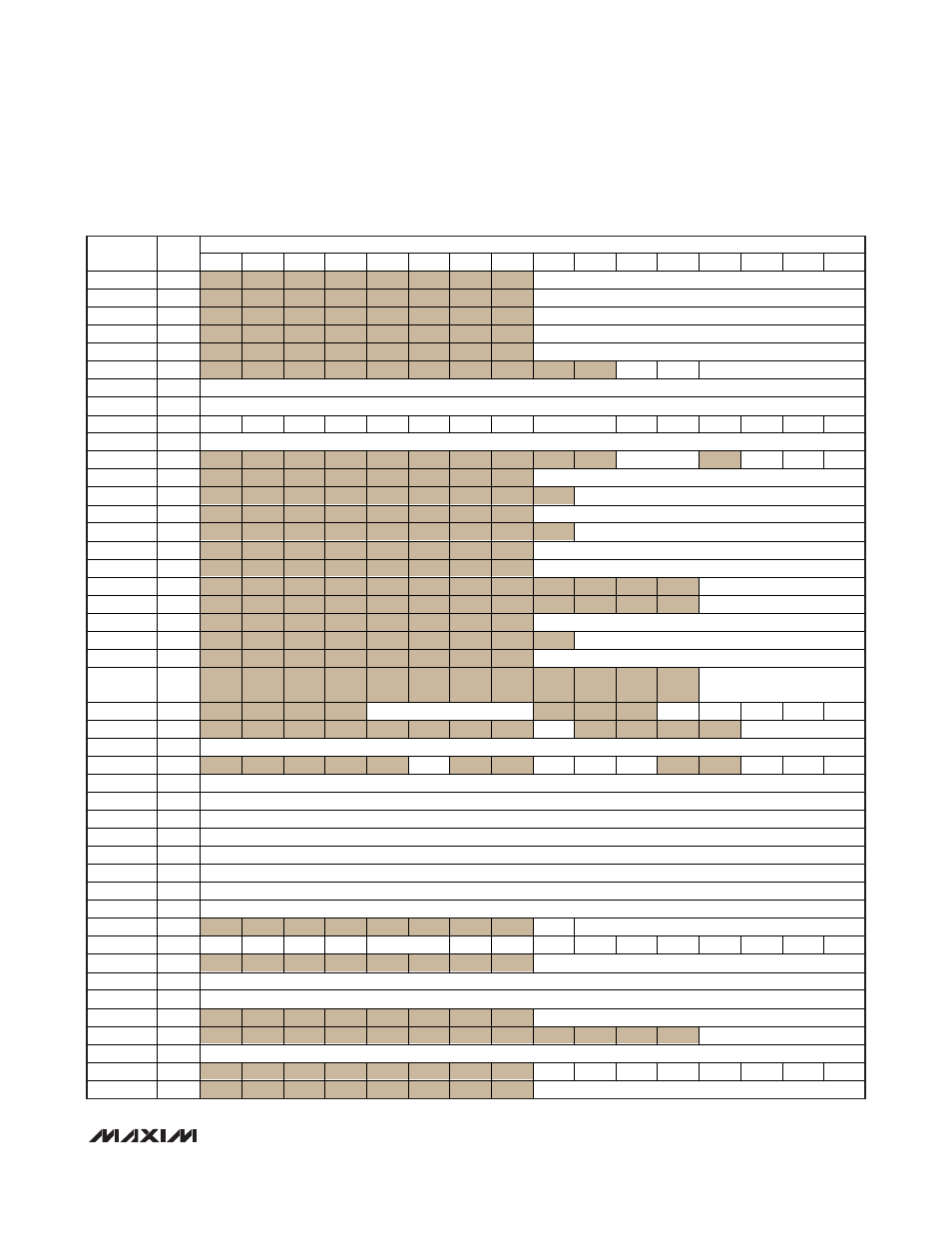

BIT

REGISTER

MOD:

REG

15

14

13

12

11

10 9 8 7 6 5 4 3 2 1 0

AD1LSB 0:9

ADC1 Output Register LSB

AD2LSB 0:10

ADC2 Output Register LSB

AD3LSB 0:11

ADC3 Output Register LSB

AD4LSB 0:12

ADC4 Output Register LSB

AD5LSB 0:13

ADC5 Output Register LSB

MREQ0 0:14

REQCDV

RSPIE REQCM

MREQ1

0:15

Master Request Register 1

MREQ2

0:16

Master Request Register 2

ADCN 0:17

IFCSEL

IF54E IF32E IF10E

MDCKS

MD2E MD1E MD0E

OSR

ABF5 ABF4 ABF3 ABF2 ABF1 ABF0

ADCC

0:18

ADC Clock Correction Register

MSTC 0:19

CCSL

MD2SNC MD1SNC MD0SNC

PO0 1:0

Port

0

Output

Register

PO1 1:1

Port

1

Output

Register

PI0 1:2

Port 0 Input Register

PI1 1:3

Port 1 Input Register

EIF0 1:4

Port 0 Interrupt Flag Register

EIE0 1:5

Port 0 Interrupt Enable Register

EIF1 1:6

Port 1 Interrupt Flag Register

EIE1 1:7

Port 1 Interrupt Enable Register

PD0 1:8

Port 0 Direction Register

PD1 1:9

Port 1 Direction Register

EIES0 1:10

Port 0 External Interrupt Edge Select

EIES1 1:11

Port 1 External Interrupt Edge

Select

SVM 1:12

SVTH

SVMSTOP

SVMI SVMIE

SVMRDY

SVMEN

FCNTL 1:13

FBUSY

FC

FDATA 1:14

Flash

Data

Register

PWCN 1:15

ENDSP

BOD

REGEN

RSTD

ECLKO

FLOCK

FLLEN

BB0

1:16

Battery-Backed General-Purpose Storage 0

BB1

1:17

Battery-Backed General-Purpose Storage 1

BB2

1:18

Battery-Backed General-Purpose Storage 2

BB3

1:19

Battery-Backed General-Purpose Storage 3

BB4

1:20

Battery-Backed General-Purpose Storage 4

BB5

1:21

Battery-Backed General-Purpose Storage 5

BB6

1:22

Battery-Backed General-Purpose Storage 6

BB7

1:23

Battery-Backed General-Purpose Storage 7

RTRM 1:24

TSGN

TRM

RCNT 1:25

WE

X32D

32KRDY 32KBYP

32KMD

FT SQE ALSF ALDF RDYE RDY BUSY ASE ADE RTCE

RTSS 1:26

RTC Subsecond Counter

RTSH

1:27

RTC Seconds Register MSW

RTSL

1:28

RTC Seconds Register LSW

RSSA 1:29

RTC

Subsecond

Alarm

RASH 1:30

RTC Seconds Alarm MSW

RASL

1:31

RTS Seconds Alarm LSW

T2CNA 2:0

ET2

T2OE0

T2POL0

TR2L

TR2

CPRL2

SS2

G2EN

T2H 2:1

Timer

2

MSB

Table 1. UserCore Peripheral Registers (continued)