Maxq3108 low-power, dual-core microcontroller – Rainbow Electronics MAXQ3108 User Manual

Page 48

MAXQ3108

Low-Power, Dual-Core Microcontroller

48

______________________________________________________________________________________

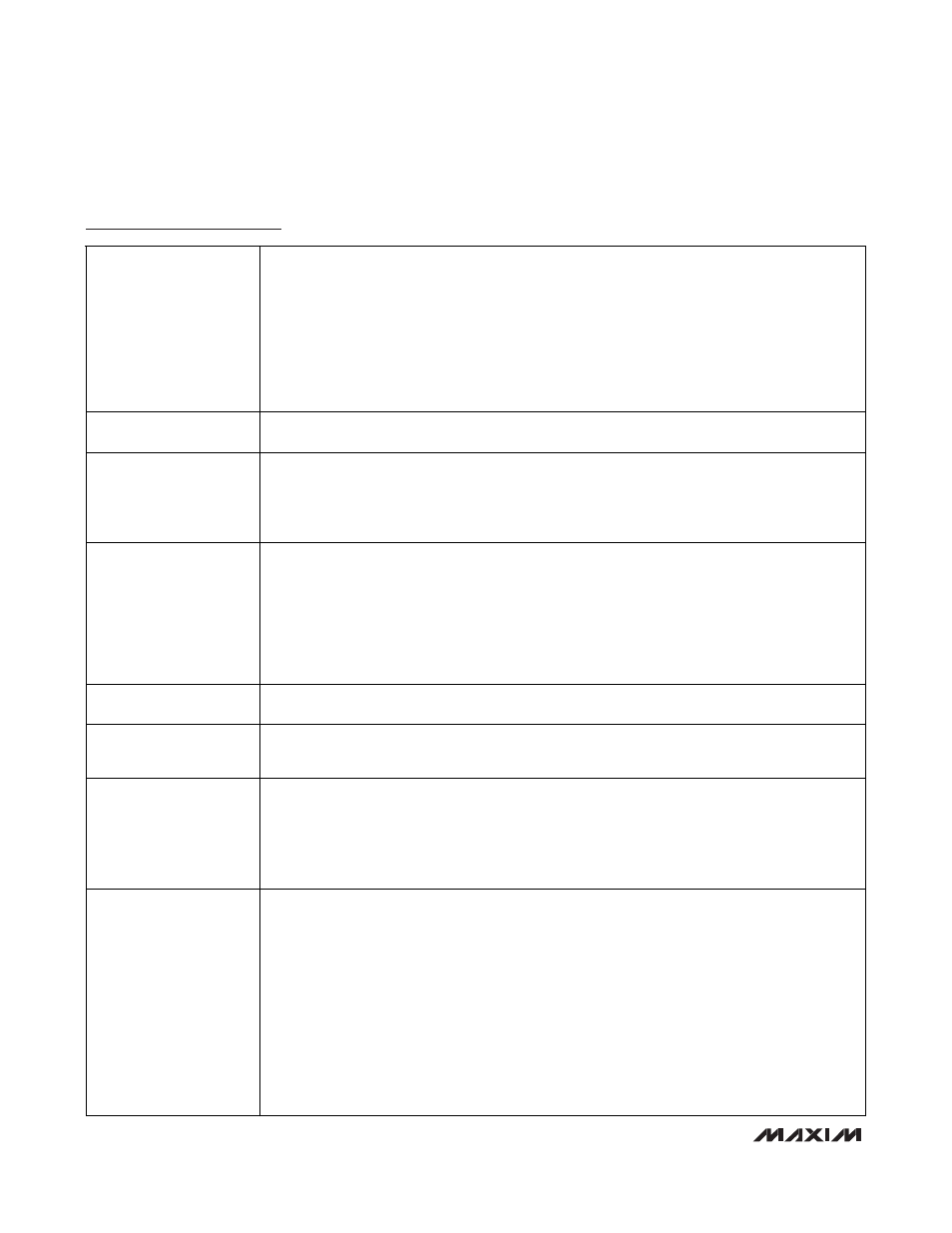

Special Function Register Bit Descriptions (continued)

I2CCN (0Ch, 04h)

I

2

C Control Register (16-Bit Register)

Initialization:

This register is cleared to 0000h on all forms of reset. The I2CSTART and I2CSTOP bits are reset to

0 when I2CMST = 0 or when I2CEN = 0. I2CSTART and I2CSTOP are mutually exclusive

operations. User software can only set one of these bits at any given time. I2CRST is reset to 0

when I2CEN = 0.

Read/Write Access:

Unrestricted read. Unrestricted write access when I2CBUSY = 0. Writes to I2CMST, I2CMODE are

ignored when I2CBUSY = 1. Writes to I2CEN are normally disabled when I2CBUSY = 1. However,

when I2CRST = 1, I2CEN can be written to even when I2CBUSY = 1. Writes to I2CACK are ignored

when I2CRST = 1.

I2CCN.0: I2CEN

I

2

C Enable. This bit enables the I

2

C function. When set to 1, the I

2

C communication unit is

enabled. When cleared to 0, the I

2

C function is disabled.

I2CCN.1: I2CMST

I

2

C Master Mode Enable. The I2CMST bit functions as a master mode enable bit for the I

2

C

module. When the I2CMST bit is set to 1, the I2C operates as a master. When the I2CMST is

cleared to 0, the I

2

C module operates in slave mode. This bit is automatically cleared whenever

the I

2

C controller receives a slave address match (I2CAMI = 1), loses arbitration (I2CALI = 1), or

receives a general call (I2CGCI = 1).

I2CCN.2: I2CMODE

I

2

C Transfer Mode. The transfer mode bit selects the direction of data transfer with respect to the

master. When the I2CMODE bit is set to 1, the master is operating in receiver mode (reading from

slave). When the I2CMODE bit is cleared to 0, the master is operating in transmitter mode (writing

to slave). Note that software writing to this bit is prohibited in slave mode. When operating in

master mode, software configures this bit to the desired direction of data transfer. When operating

in slave mode, the direction of data transfer is determined by the R/W bit received during the

address stage and this bit reflects the actual R/W bit value in the current transfer and is set by

hardware. Software writing to this bit in slave mode is ignored.

I2CCN.3: Reserved

Reserved. Do not write a 1 to this location. Functionally, this is the I2CEA bit, however, there are

problems with the I

2

C extended addressing mode.

I2CCN.4: I2CSTRS

I

2

C Clock Stretch Select. Setting this bit to 1 enables clock stretching after the falling edge of the

8th clock cycle. Clearing this bit to 0 enables clock stretching after the falling edge of the 9th

clock cycle. This bit has no effect when clock stretching is disabled (I2CSTREN = 0).

I2CCN.5: I2CACK

I

2

C Data Acknowledge Bit. This bit selects the acknowledge bit returned by the I

2

C controller while

acting as a receiver. Setting this bit to 1 generates a NACK (leaving SDA high). Clearing the

I2CACK bit to 0 generates an ACK (pulling SDA LOW) during the acknowledgement cycle. This bit

retains its value unless changed by software or hardware. When an I

2

C abort is in progress

(I2CRST = 1), this bit is set to 1 by hardware and software writes to this bit are ignored when

I2CRST = 1.

I2CCN.6: I2CSTART

I

2

C START Enable. Setting this bit automatically generates a START condition when the bus is free

or generates a repeated START condition during a transfer where the I

2

C module is operating as the

master. This bit is automatically self-cleared to 0 after the START condition has been generated. If

the I

2

C START interrupt is enabled, a START condition generates an interrupt to the CPU.

In master mode, setting this bit could also start the timeout timer if enabled. If the timeout timer

expires before the START condition can be generated, a timeout interrupt is generated to the CPU if

enabled. The I2CSTART bit is also cleared to 0 by the timeout event.

Note that this bit has no effect when the I

2

C is operating in slave mode (I2CMST = 0) and is reset

to 0 when I2CMST = 0 or I2CEN = 0. Also, the I2CSTART and I2CSTOP are mutually exclusive. If

both bits are set at the same time, it is considered as an invalid operation and the I

2

C controller

ignores the request and resets both bits to 0. Setting the I2CSTART bit to 1 while I2CSTOP = 1 is an

invalid operation and is ignored, leaving the I2CSTART bit cleared to 0.