Maxq3108 low-power, dual-core microcontroller – Rainbow Electronics MAXQ3108 User Manual

Page 49

MAXQ3108

Low-Power, Dual-Core Microcontroller

______________________________________________________________________________________

49

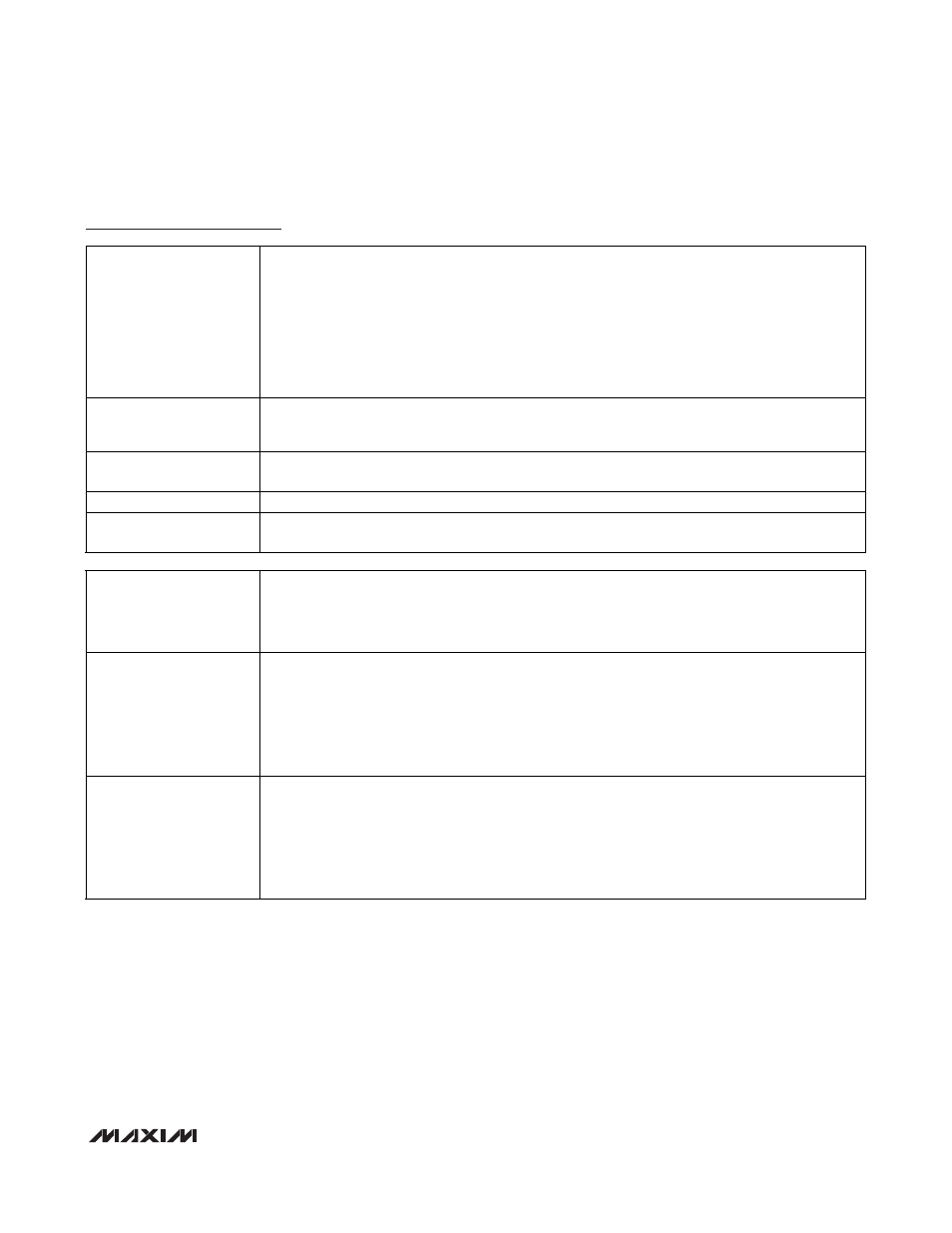

Special Function Register Bit Descriptions (continued)

I2CCN.7: I2CSTOP

I

2

C STOP Enable. Setting this bit to 1 generates a STOP condition. This bit is automatically self-

cleared to 0 after the STOP condition has been generated. In master mode, setting this bit could

also start the timeout timer if enabled. If the timeout timer expires before the STOP condition can be

generated, a timeout interrupt is generated to the CPU if enabled. The I2CSTOP bit is also cleared

to 0 by the timeout event.

Note that this bit has no effect when the I

2

C is operating in slave mode (I2CMST = 0) and is reset

to 0 when I2CMST = 0 or I2CEN = 0. Setting the I2CSTOP bit to 1 while I2CSTART = 1 is an invalid

operation and is ignored, leaving the I2CSTOP bit cleared to 0.

I2CCN.8: I2CGCEN

I

2

C General Call Enable. Setting this bit to 1 enables the I

2

C bus to respond to a general call

address (address = 0000 0000). Clearing this bit to 0 disables the response to a general call

address.

I2CCN.9: I2CSTREN

I

2

C Clock Stretch Enable. Setting this bit to 1 stretches the clock (hold SCL low) at the end of the

clock cycle specified in I2CSTRS. Clearing this bit disables clock stretching.

I2CCN.[14:10]: Reserved

Reserved. Reads return 0.

I2CCN.15: I2CRST

I

2

C Reset. Setting this bit to 1 aborts the current transaction and resets the I

2

C controller. This bit is

set to 1 by software and is only cleared to 0 by hardware after the reset or when I2CEN = 0.

I2CCK (0Dh, 04h)

I

2

C Clock Control Register (16-Bit Register)

Initialization:

This register is set to 0204h on all forms of reset.

Read/Write Access:

Unrestricted read. Write to this register is allowed only when I2CBUSY = 0. This register has no

function when operating in slave mode and the clock generation circuitry should be disabled.

I2CCK.[7:0]: I2CCKL[7:0]

I

2

C Clock Low Bits 7:0. These bits define the I

2

C SCL low period in a number of system clocks,

with bit 7 as the most significant bit. The duration of SCL low time is calculated using the following

equation:

I

2

C Low Time Period = System Clock x (I2CCKL[7:0] + 1)

When operating in master mode, the I2CCKL must be set to a minimum value of four to ensure

proper operation. Any value less than four is set to four.

I2CCK.[15:8]: I2CCKH[7:0]

I

2

C Clock High Bits 7:0. These bits define the I

2

C SCL high period in a number of system clocks,

with bit 7 as the most significant bit. The duration of SCL high time is calculated using the

following equation:

I

2

C High Time Period = System Clock x (I2CCKH[7:0] + 1)

When operating in master mode, the I2CCKH must be set to a minimum value of two to ensure

proper operation. Any value less than two is set to two.