Maxq3108 low-power, dual-core microcontroller – Rainbow Electronics MAXQ3108 User Manual

Page 42

MAXQ3108

Low-Power, Dual-Core Microcontroller

42

______________________________________________________________________________________

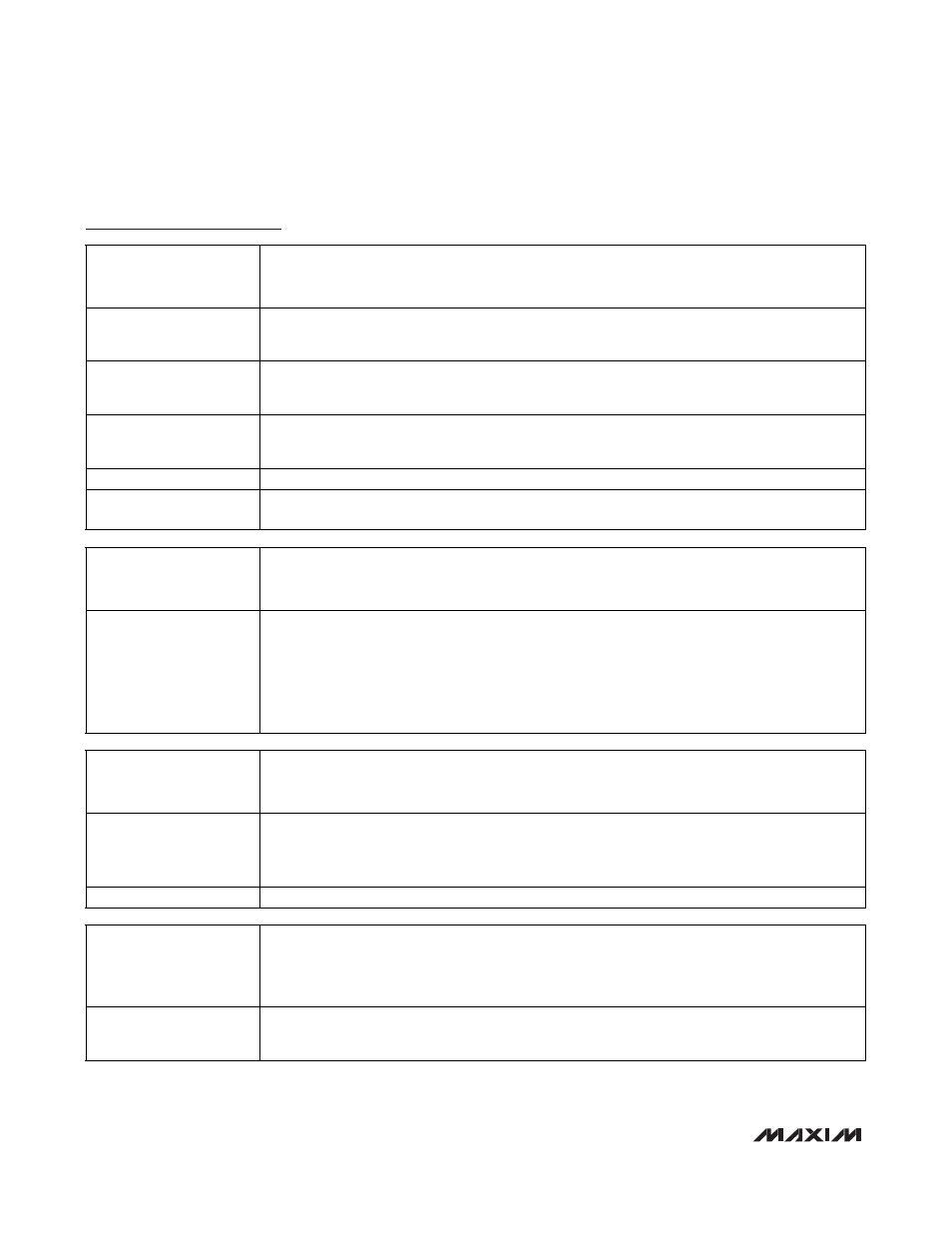

Special Function Register Bit Descriptions (continued)

SPICF (0Eh, 03h)

SPI Configuration Register

Initialization:

This buffer is cleared to 00h on all forms of reset.

Read/Write Access: Unrestricted

read/write.

SPICF.0: CKPOL

Clock Polarity Select. This bit is used with the CKPHA bit to determine the SPI transfer format.

When the CKPOL is set to 1, the SPI uses the clock falling edge as an active edge. When the

CKPOL is cleared to 0, the SPI selects the clock rising edge as an active edge.

SPICF.1: CKPHA

Clock Phase Select. This bit is used with the CKPOL bit to determine the SPI transfer format. When

the CKPHA is set to 1, the SPI samples input data at an inactive edge. When the CKPHA is cleared

to 0, the SPI samples input data at an active edge.

SPICF.2: CHR

Character Length Bit. The CHR bit determines the character length for an SPI transfer cycle. A

character can consist of 8 or 16 bits in length. When CHR bit is 0, the character is 8 bits; when

CHR is set to 1, the character is 16 bits.

SPICF.[6:3]: Reserved

Reserved. Reads return 0.

SPICF.7: ESPII

SPI Interrupt Enable. Setting this bit to 1 enables the SPI interrupt when the MODF, WCOL, ROVR,

or SPIC flags are set. Clearing this bit to 0 disables the SPI interrupt.

SPICK (0Fh, 03h)

SPI Clock Register

Initialization:

This buffer is cleared to 00h on all forms of reset.

Read/Write Access: Unrestricted

read/write.

SPICK.[7:0]:

Clock Divide Ratio Bit 7:0. These bits select one of the 256 divide ratios (0 to 255) used for the

baud-rate generator, with bit 7 as the most significant bit. The frequency of the SPI baud rate is

calculated using the following equation:

SPI Baud Rate = 0.5 x System Clock/(Divide Ratio + 1)

This register has no function when operating in slave mode, and the clock generation circuitry

should be disabled.

I2CBUF (00h, 04h)

I

2

C Data Buffer Register (16-Bit Register)

Initialization:

This register is cleared to 0000h on all forms of resets.

Read/Write Access:

Unrestricted read access. This register can be written to only when I2CBUSY = 0.

I2CBUF.[9:0]:

I2C Data Buffer Bits 9:0. Data for I

2

C transfer is read from or written to this location. The I

2

C

transmit and receive buffers are separate but both are addressed at this location. During address

transmission, I2CBUF[6:0] is used as the address bits. During data transmission, only I2CBUF[7:0]

is used.

I2CBUF.[15:10]: Reserved

Reserved. Reads return 0.

I2CST (01h, 04h)

I

2

C Status Register (16-Bit Register)

Initialization:

This register is cleared to 0000h on all forms of reset.

Read/Write Access:

Unrestricted read. Not all the bits can be written by software. For each bit accessibility, see the

individual bit description.

I2CST.0: I2CSRI

I

2

C START Interrupt Flag. This bit is set to 1 when a START condition (S or Sr) is detected. This bit

must be cleared to 0 by software once set. Setting this bit to 1 by software causes an interrupt if

enabled.