Maxq3108 low-power, dual-core microcontroller – Rainbow Electronics MAXQ3108 User Manual

Page 24

MAXQ3108

Low-Power, Dual-Core Microcontroller

24

______________________________________________________________________________________

Special Function Register Bit Descriptions (continued)

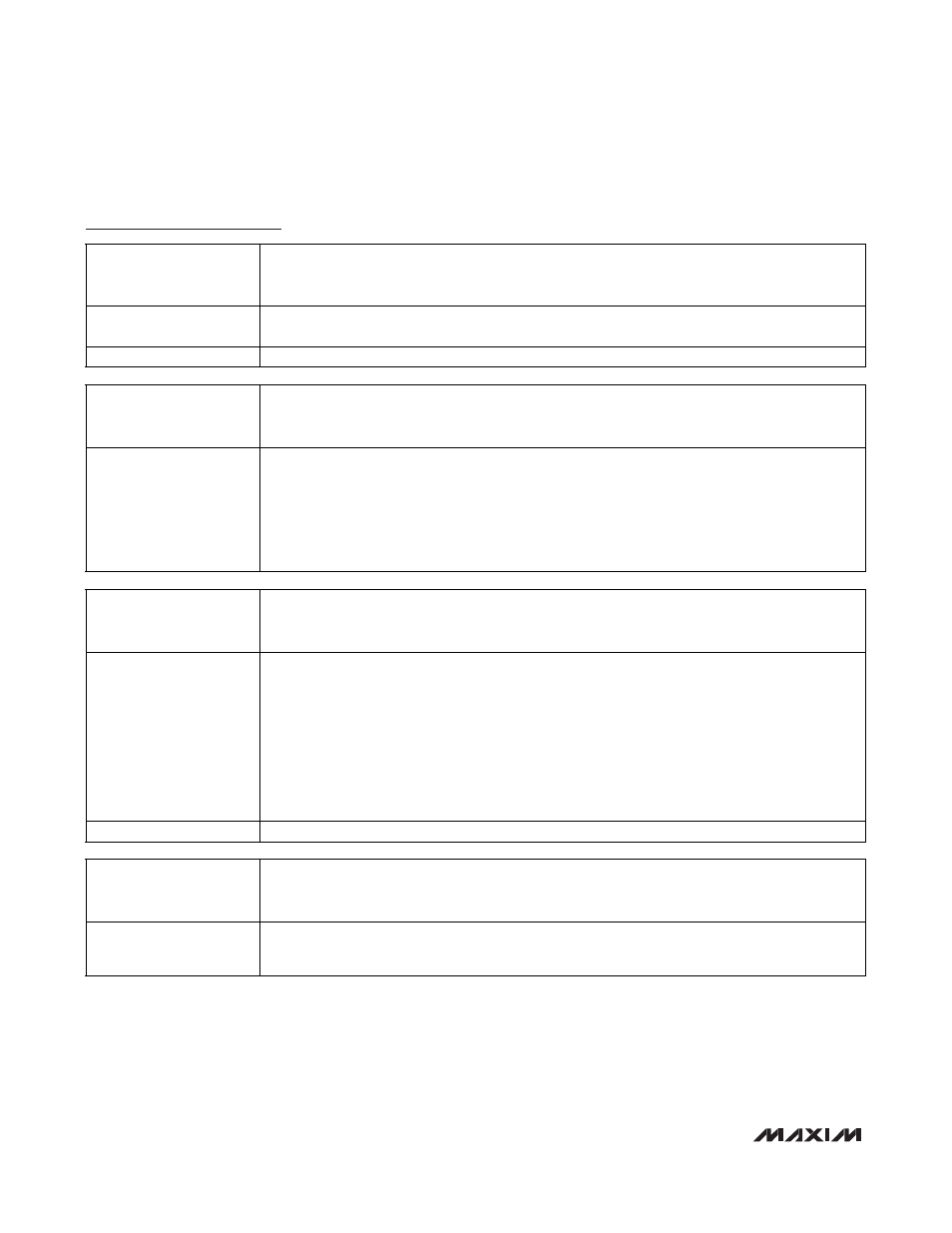

EIE1 (07h, 01h)

External Interrupt Enable 1 Register

Initialization:

EIE1 is cleared to 00h on all forms of reset.

Read/Write Access: Unrestricted

read/write.

EIE1.[3:0]: EX[11:8]

Enable External Interrupt Bits 11:8. Setting any of these bits to 1 enables the corresponding

external interrupt. Clearing any of the bits to 0 disables the corresponding interrupt function.

EIE1.[7:4]: Reserved

Reserved. Reads return 0.

PD0 (08h, 01h)

Port 0 Direction Register

Initialization:

This register is cleared to 00h on all forms of reset.

Read/Write Access: Unrestricted

read/write.

PD0.[7:0]:

Port 0 Direction Register Bits 7:0. PD0 is used to determine the direction of the Port 0 function. The

port pins are independently controlled by their direction bits. When a bit is set to 1, its corresponding

pin is used as an output; data in the PO register is driven on the pin. When a bit is cleared to 0, its

corresponding pin is used as an input, and allows an external signal to drive the pin. Note that each

port pin has a weak pullup circuit when functioning as an input and the p-channel pullup transistor is

controlled by its respective PO bits. If the PO bit is set to 1, the weak pullup is on; if the PO bit is

cleared to 0, the weak pullup is off and forces the port pin into three-state.

PD1 (09h, 01h)

Port 1 Direction Register

Initialization:

This register is cleared to 00h on all forms of reset.

Read/Write Access: Unrestricted

read/write.

PD1.[6:0]:

Port 1 Direction Register Bits 6:0. PD1 is used to determine the direction of the port 1 function.

The port pins are independently controlled by their direction bit. When a bit is set to 1, its

corresponding pin is used as an output; data in the PO register is driven on the pin. When a bit is

cleared to 0, its corresponding pin is used as an input, and allows an external signal to drive the

pin. Note that each port pin has a weak pullup circuit when functioning as an input and the p-

channel pullup transistor is controlled by its respective PO bits. If the PO bit is set to 1, the weak

pullup is on; if the PO bit is cleared to 0, the weak pullup is off and forces the port pin into three-

state. Special note about P1.6: The RST input function remains enabled on P1.6 unless it is

explicitly disabled (RSTD = 1). This means that the ports control bits (PD, PO) can be used to

generate a reset (e.g., by driving the pin low).

PD1.7: Reserved

Reserved. Reads return 0.

EIES0 (0Ah, 01h)

External Interrupt Edge Select 0 Register

Initialization:

EIES0 is cleared to 00h on all forms of reset.

Read/Write Access: Unrestricted

read/write.

EIES0.[7:0]: IT[7:0]

Edge Select for External Interrupt Bits 7:0

ITx = 0: External interrupt x is positive-edge triggered.

ITx = 1: External interrupt x is negative-edge triggered.