Texas Instruments TSB12LV26 User Manual

Page 78

4–40

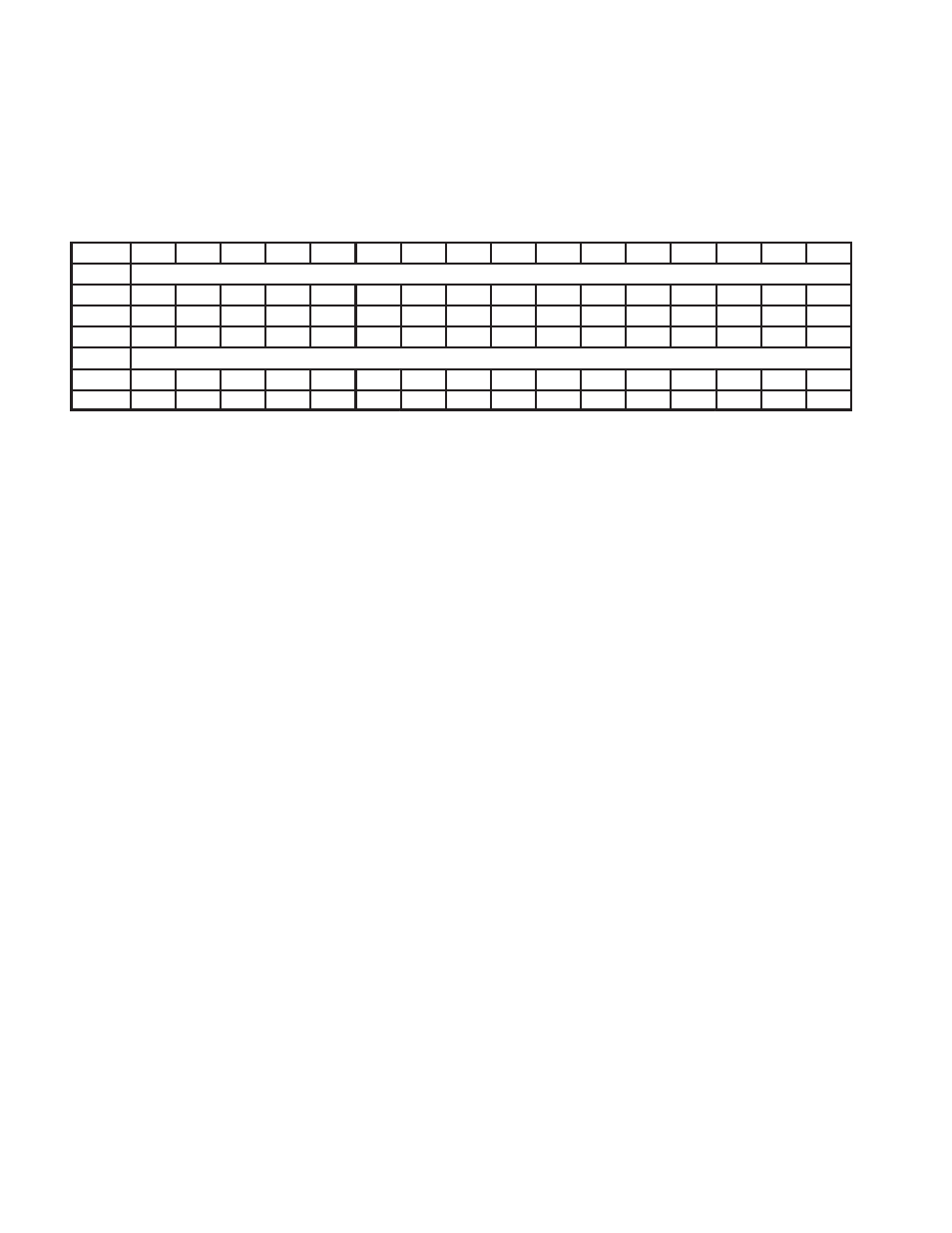

4.42 Isochronous Receive Context Command Pointer Register

The isochronous receive context command pointer register contains a pointer to the address of the first descriptor

block that the TSB12LV26 accesses when software enables an isochronous receive context by setting the

isochronous receive context control register (see Section 4.41) bit 15 (run). The n value in the following register

addresses indicates the context number (n = 0, 1, 2, 3).

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Isochronous receive context command pointer

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Isochronous receive context command pointer

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

Register:

Isochronous receive context command pointer

Type:

Read-only

Offset:

40Ch + (32 * n)

Default:

XXXX XXXXh

- Digital Signal Processor SM320F2812-HT (153 pages)

- MSP430x1xx (440 pages)

- Laser And Motor Drives DRV8811EVM (13 pages)

- TMS320 DSP (88 pages)

- MSP430x11x1 (45 pages)

- TVP5154EVM (55 pages)

- TMS320DM646X DMSOC (64 pages)

- CC2511 (24 pages)

- SN65HVS880 (4 pages)

- TPS650231EVM (14 pages)

- TMS320TCI648x (256 pages)

- TSC2007EVM-PDK (16 pages)

- UCC38500EVM (16 pages)

- TMS320C6000 (62 pages)

- SCAU020 (21 pages)

- TPS40051 (17 pages)

- TNETE2201 (14 pages)

- TMS320C64x DSP (306 pages)

- UCC2891 (21 pages)

- TMS320C3x (757 pages)

- MSP430 (138 pages)

- TMS320C6712D (102 pages)

- MSP430x4xx (512 pages)

- TMS320C6454 (225 pages)

- SPRU938B (48 pages)

- TUSB3210 (22 pages)

- TMS320C6457 (43 pages)

- CC2530ZNP (3 pages)

- TMS320C6455 (50 pages)

- TMS320C6472 (2 pages)

- VLYNQ Port (49 pages)

- TMS380C26 (92 pages)

- MSP-FET430 (95 pages)

- TMS320TCI6486 (160 pages)

- TPS2330 (22 pages)

- DM648 DSP (47 pages)

- TMS320DM36X (134 pages)

- MSC1211 (35 pages)

- SPRAA56 (29 pages)

- DAC7741EVM (28 pages)

- CDCM7005 (34 pages)

- TMS370 (99 pages)

- Adpater (37 pages)

- TMS320C6452 DSP (46 pages)