14 min_gnt and max_lat register, 15 ohci control register – Texas Instruments TSB12LV26 User Manual

Page 30

3–10

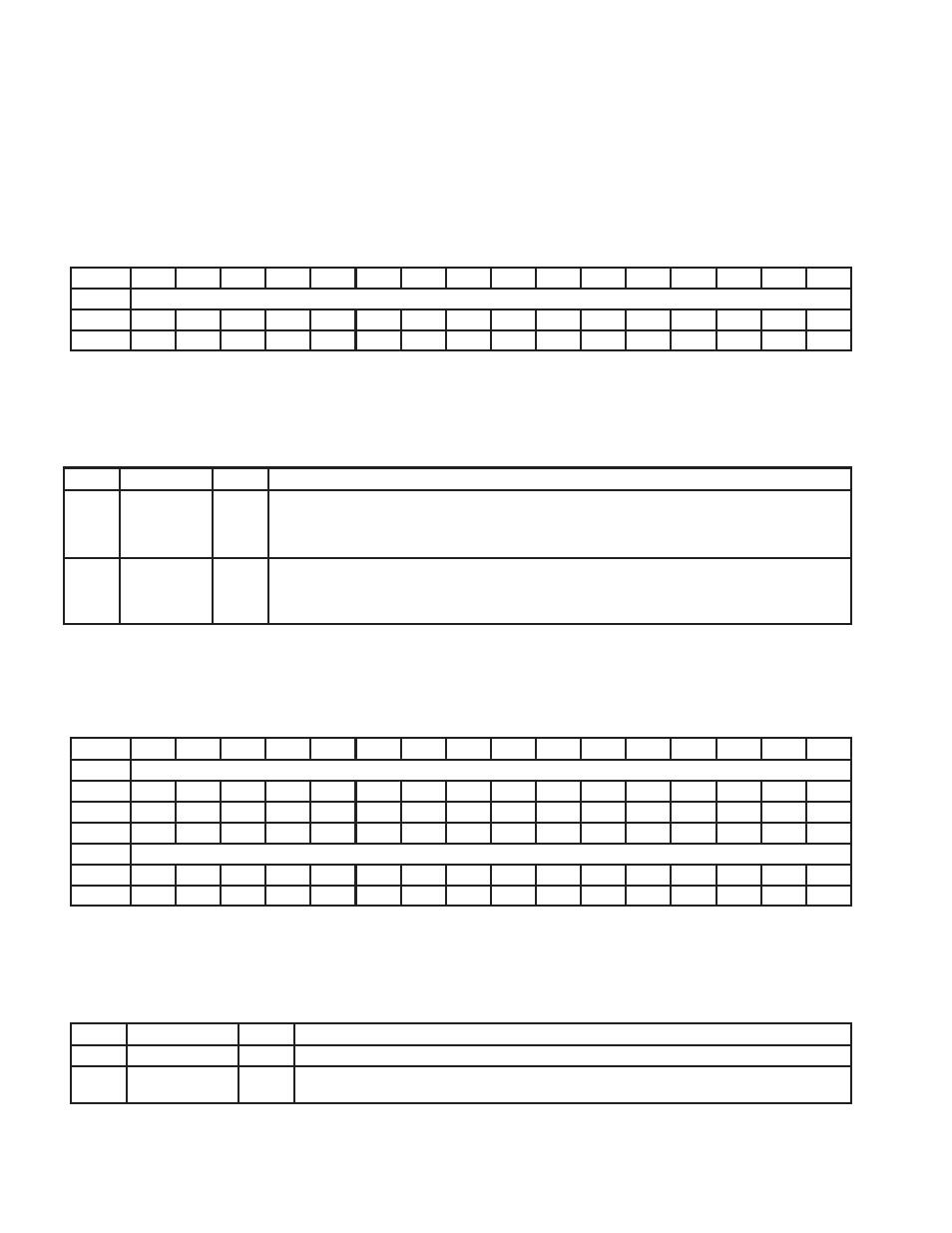

3.14 MIN_GNT and MAX_LAT Register

The MIN_GNT and MAX_LAT register is used to communicate to the system the desired setting of bits 15–8 of the

latency timer and class cache line size register (offset 0Ch, see Section 3.7). If a serial ROM is detected, then the

contents of this register are loaded through the serial ROM interface after a PCI reset. If no serial ROM is detected,

then this register returns a default value that corresponds to the MIN_GNT = 2, MAX_LAT = 4. See Table 3–11 for

a complete description of the register contents.

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

MIN_GNT and MAX_LAT

Type

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

Default

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

Register:

MIN_GNT and MAX_LAT

Type:

Read/Update

Offset:

3Eh

Default:

0402h

Table 3–11. MIN_GNT and MAX_LAT Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

15–8

MAX_LAT

RU

Maximum latency. The contents of this register may be used by host BIOS to assign an arbitration

priority-level to the TSB12LV26. The default for this register indicates that the TSB12LV26 may need to

access the PCI bus as often as every 0.25

µ

s; thus, an extremely high priority level is requested. The

contents of this field may also be loaded through the serial ROM.

7–0

MIN_GNT

RU

Minimum grant. The contents of this register may be used by host BIOS to assign a latency timer and class

cache line size register (offset 0Ch, see Section 3.7) value to the TSB12LV26. The default for this register

indicates that the TSB12LV26 may need to sustain burst transfers for nearly 64

µ

s; thus, requesting a large

value be programmed in bits 15–8 of the TSB12LV26 latency timer and class cache line size register.

3.15 OHCI Control Register

The OHCI control register is defined by the

1394 Open Host Controller Interface Specification and provides a bit for

big endian PCI support. See Table 3–12 for a complete description of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

OHCI control

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

OHCI control

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R/W

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Register:

OHCI control

Type:

Read/Write

Offset:

40h

Default:

0000 0000h

Table 3–12. OHCI Control Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31–1

RSVD

R

Reserved. Bits 31–1 return 0s when read.

0

GLOBAL_SWAP

R/W

When this bit is set, all quadlets read from and written to the PCI interface are byte swapped (big

endian). This bit is loaded from ROM and should be programmed to 0 for normal operation.