37 asynchronous context control register – Texas Instruments TSB12LV26 User Manual

Page 73

4–35

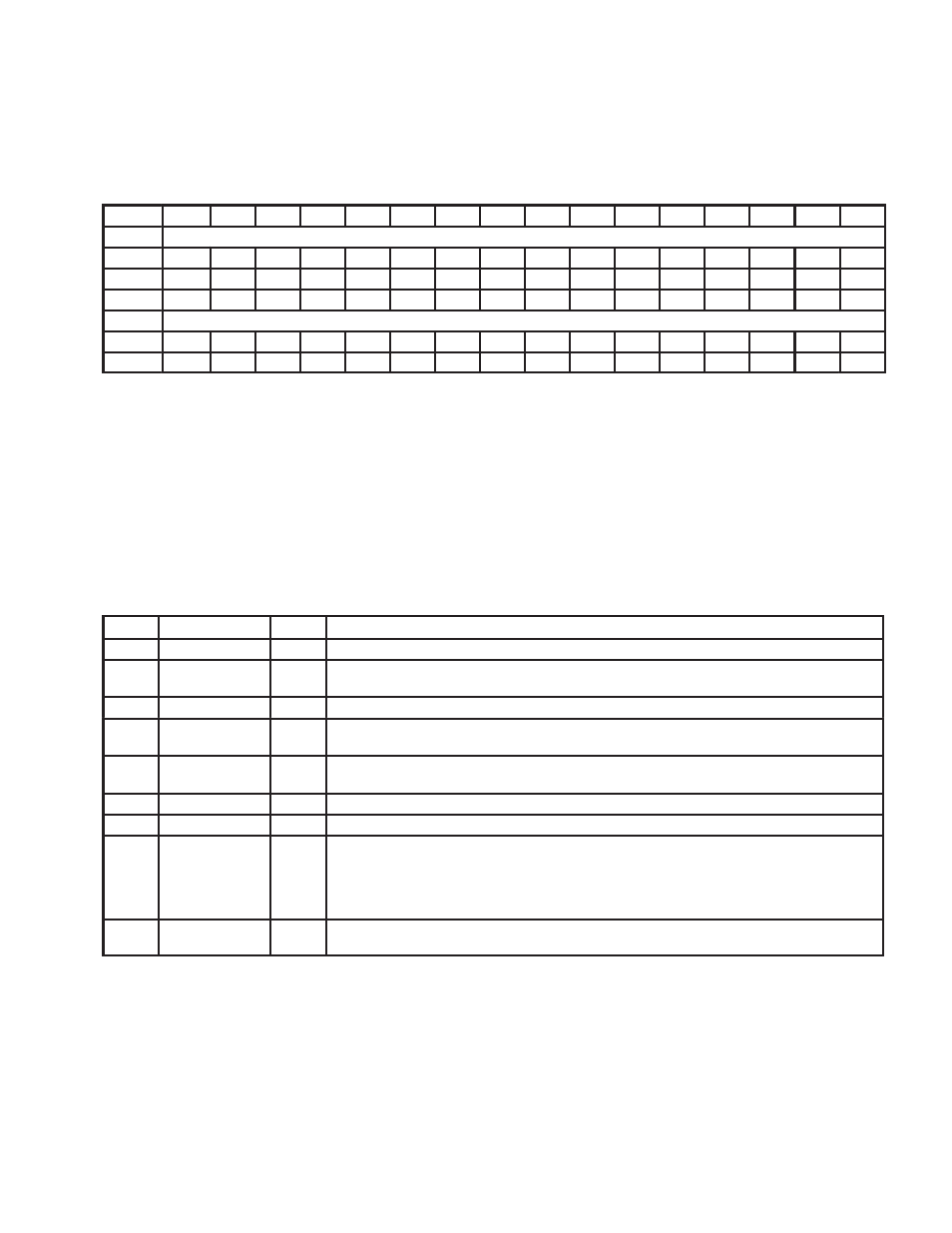

4.37 Asynchronous Context Control Register

The asynchronous context control set/clear register controls the state and indicates status of the DMA context. See

Table 4–27 for a complete description of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Asynchronous context control

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Asynchronous context control

Type

RSCU

R

R

RSU

RU

RU

R

R

RU

RU

RU

RU

RU

RU

RU

RU

Default

0

0

0

X

0

0

0

0

X

X

X

X

X

X

X

X

Register:

Asynchronous context control

Type:

Read/Set/Clear/Update, Read/Set/Update, Read/Update, Read-only

Offset:

180h

set register

[ATRQ]

184h

clear register

[ATRQ]

1A0h

set register

[ATRS]

1A4h

clear register

[ATRS]

1C0h

set register

[ARRQ]

1C4h

clear register

[ARRQ]

1E0h

set register

[ARRS]

1E4h

clear register

[ARRS]

Default:

0000 X0XXh

Table 4–27. Asynchronous Context Control Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31–16

RSVD

R

Reserved. Bits 31–16 return 0s when read.

15

run

RSCU

This bit is set by software to enable descriptor processing for the context and cleared by software to

stop descriptor processing. The TSB12LV26 changes this bit only on a hardware or software reset.

14–13

RSVD

R

Reserved. Bits 14–13 return 0s when read.

12

wake

RSU

Software sets this bit to cause the TSB12LV26 to continue or resume descriptor processing. The

TSB12LV26 clears this bit on every descriptor fetch.

11

dead

RU

The TSB12LV26 sets this bit when it encounters a fatal error and clears the bit when software resets

bit 15 (run).

10

active

RU

The TSB12LV26 sets this bit to 1 when it is processing descriptors.

9–8

RSVD

R

Reserved. Bits 9–8 return 0s when read.

7–5

spd

RU

This field indicates the speed at which a packet was received or transmitted, and only contains

meaningful information for receive contexts. This field is encoded as:

000 = 100 Mbits/sec,

001 = 200 Mbits/sec, and

010 = 400 Mbits/sec. All other values are reserved.

4–0

eventcode

RU

This field holds the acknowledge sent by the link core for this packet, or holds an internally generated

error code if the packet was not transferred successfully.