22 interrupt mask register – Texas Instruments TSB12LV26 User Manual

Page 57

4–19

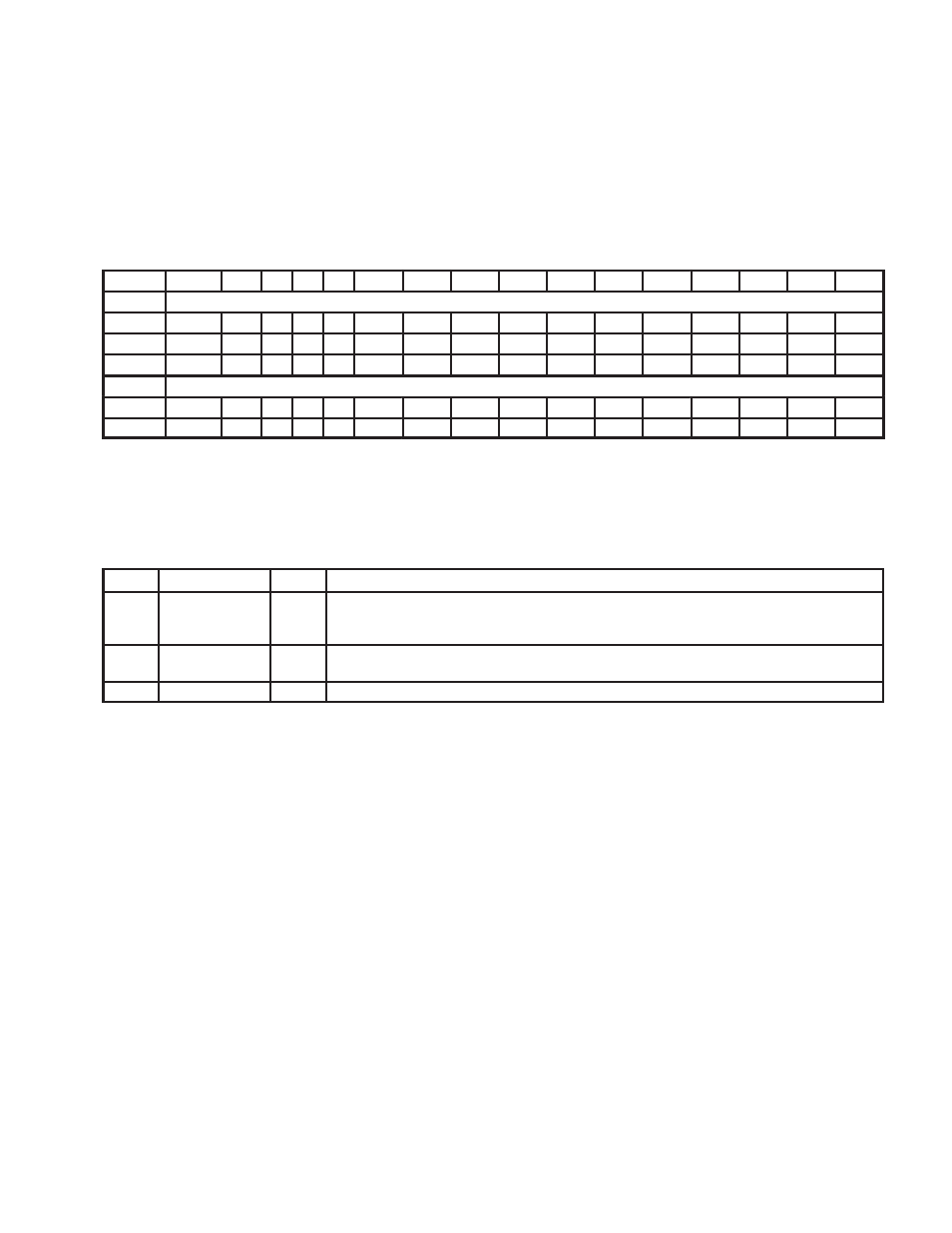

4.22 Interrupt Mask Register

The interrupt mask set/clear register is used to enable the various TSB12LV26 interrupt sources. Reads from either

the set register or the clear register always return the contents of the interrupt mask register. In all cases except

masterIntEnable (bit 31) and VendorSpecific (bit 30), the enables for each interrupt event align with the interrupt event

register bits detailed in Table 4–14. See Table 4–15 for a description of bits 31 and 30.

This register is fully compliant with OHCI and the TSB12LV26 adds an OHCI 1.0 compliant interrupt function to bit 30.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Interrupt mask

Type

RSCU

RSC

R

R

R

RSCU

RSCU

RSCU

RSCU

RSCU

RSCU

RSCU

RSCU

R

RSCU

RSCU

Default

X

X

0

0

0

X

X

X

X

X

X

X

X

0

X

X

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Interrupt mask

Type

R

R

R

R

R

R

RSCU

RSCU

RU

RU

RSCU

RSCU

RSCU

RSCU

RSCU

RSCU

Default

0

0

0

0

0

0

X

X

X

X

X

X

X

X

X

X

Register:

Interrupt mask

Type:

Read/Set/Clear/Update, Read/Set/Clear, Read/Update, Read-only

Offset:

88h

set register

8Ch

clear register

Default:

XXXX 0XXXh

Table 4–15. Interrupt Mask Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31

masterIntEnable

RSCU

Master interrupt enable. If this bit is set, then external interrupts are generated in accordance with the

interrupt mask register. If this bit is cleared, then external interrupts are not generated regardless of the

interrupt mask register settings.

30

vendorSpecific

RSC

When this bit is set, this vendor-specific interrupt mask enables interrupt generation when bit 30

(vendorSpecific) of the interrupt event register (OHCI offset 80h/84h, see Section 4.21) is set.

29–0

See Table 4–14.