12 power management capabilities pointer register, 13 interrupt line and pin register – Texas Instruments TSB12LV26 User Manual

Page 29

3–9

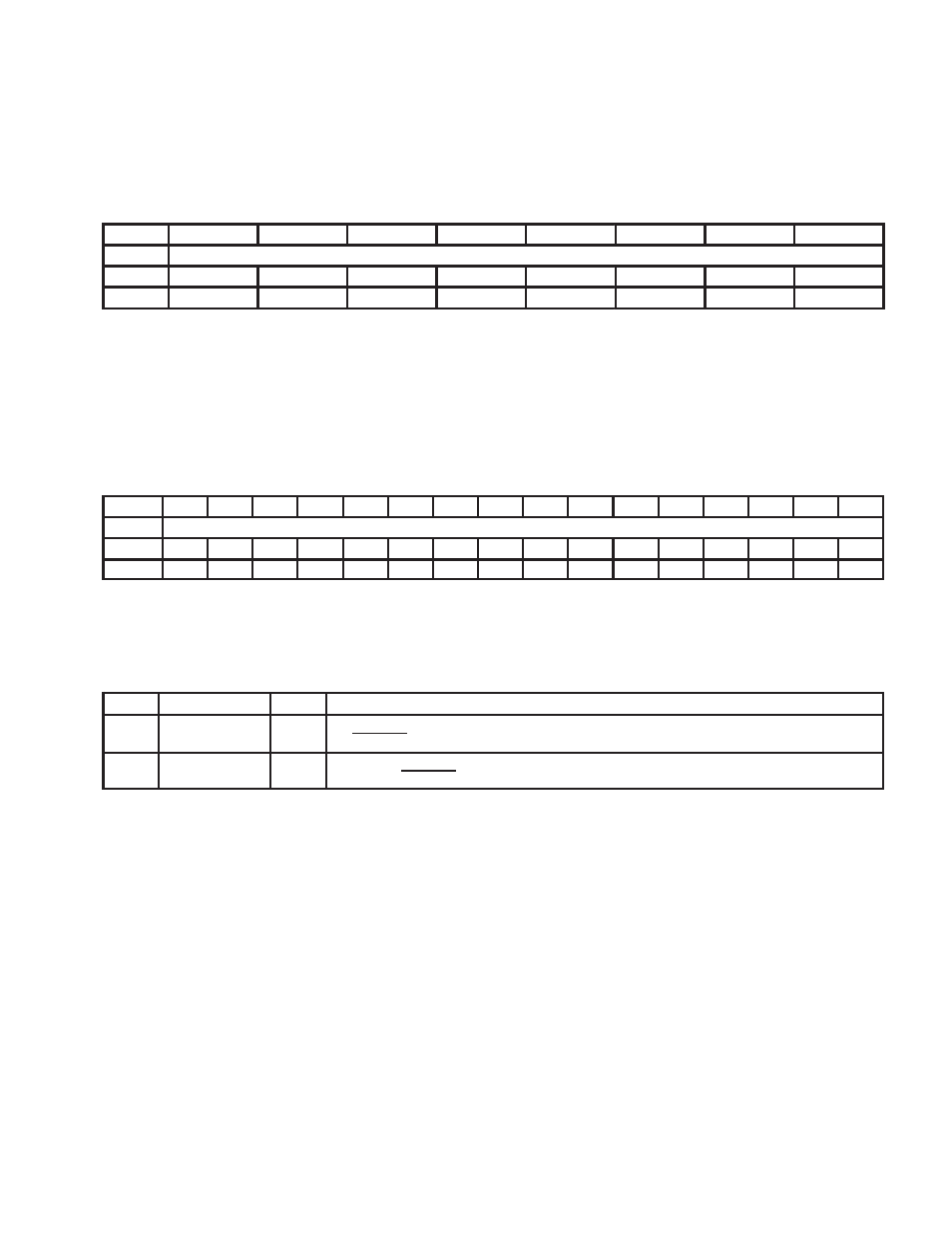

3.12 Power Management Capabilities Pointer Register

The power management capabilities pointer register provides a pointer into the PCI configuration header where the

PCI power management register block resides. The TSB12LV26 configuration header double-words at offsets 44h

and 48h provide the power management registers. This register is read-only and returns 44h when read.

Bit

7

6

5

4

3

2

1

0

Name

Power management capabilities pointer

Type

R

R

R

R

R

R

R

R

Default

0

1

0

0

0

1

0

0

Register:

Power management capabilities pointer

Type:

Read-only

Offset:

34h

Default:

44h

3.13 Interrupt Line and Pin Register

The interrupt line and pin register is used to communicate interrupt line routing information. See Table 3–10 for a

complete description of the register contents.

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Interrupt line and pin

Type

R

R

R

R

R

R

R

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

Register:

Interrupt line and pin

Type:

Read/Write, Read-only

Offset:

3Ch

Default:

0100h

Table 3–10. Interrupt Line and Pin Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

15–8

INTR_PIN

R

Interrupt pin. Returns 01h when read, indicating that the TSB12LV26 PCI function signals interrupts on

the PCI_INTA pin.

7–0

INTR_LINE

R/W

Interrupt line. This field is programmed by the system and indicates to software which interrupt line the

TSB12LV26 PCI_INTA is connected to.