23 isochronous transmit interrupt event register – Texas Instruments TSB12LV26 User Manual

Page 58

4–20

4.23 Isochronous Transmit Interrupt Event Register

The isochronous transmit interrupt event set/clear register reflects the interrupt state of the isochronous transmit

contexts. An interrupt is generated on behalf of an isochronous transmit context if an OUTPUT_LAST* command

completes and its interrupt bits are set. Upon determining that the interrupt event register (OHCI offset 80h/84h, see

Section 4.21) isochTx (bit 6) interrupt has occurred, software can check this register to determine which context(s)

caused the interrupt. The interrupt bits are set by an asserting edge of the corresponding interrupt signal, or by writing

a 1 in the corresponding bit in the set register. The only mechanism to clear a bit in this register is to write a 1 to the

corresponding bit in the clear register. See Table 4–16 for a complete description of the register contents.

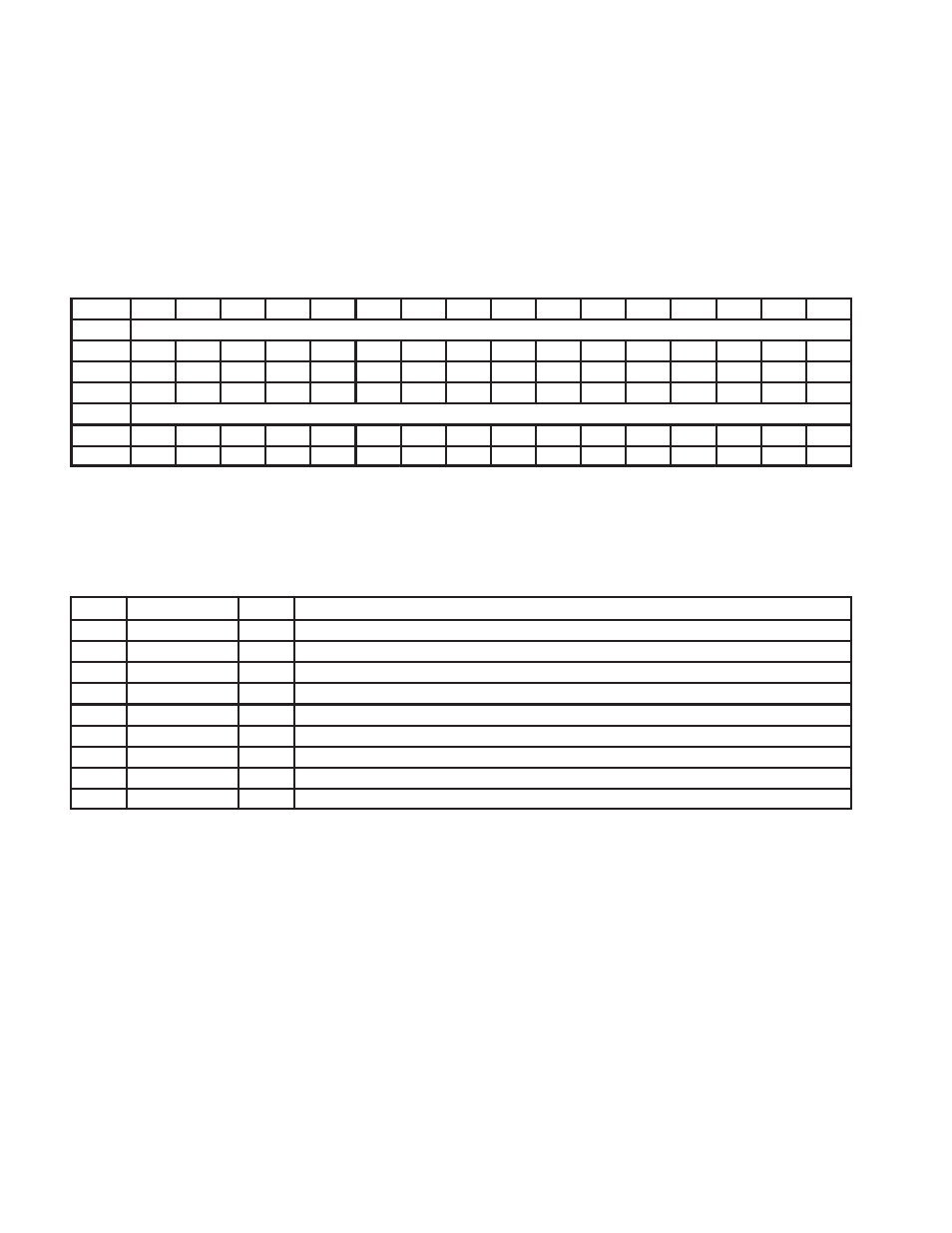

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Isochronous transmit interrupt event

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Isochronous transmit interrupt event

Type

R

R

R

R

R

R

R

R

RSC

RSC

RSC

RSC

RSC

RSC

RSC

RSC

Default

0

0

0

0

0

0

0

0

X

X

X

X

X

X

X

X

Register:

Isochronous transmit interrupt event

Type:

Read/Set/Clear, Read-only

Offset:

90h

set register

94h

clear register [returns IsoXmitEvent and IsoXmitMask when read]

Default:

0000 00XXh

Table 4–16. Isochronous Transmit Interrupt Event Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31–8

RSVD

R

Reserved. Bits 31–8 return 0s when read.

7

isoXmit7

RSC

Isochronous transmit channel 7 caused the interrupt event register bit 6 (isochTx) interrupt.

6

isoXmit6

RSC

Isochronous transmit channel 6 caused the interrupt event register bit 6 (isochTx) interrupt.

5

isoXmit5

RSC

Isochronous transmit channel 5 caused the interrupt event register bit 6 (isochTx) interrupt.

4

isoXmit4

RSC

Isochronous transmit channel 4 caused the interrupt event register bit 6 (isochTx) interrupt.

3

isoXmit3

RSC

Isochronous transmit channel 3 caused the interrupt event register bit 6 (isochTx) interrupt.

2

isoXmit2

RSC

Isochronous transmit channel 2 caused the interrupt event register bit 6 (isochTx) interrupt.

1

isoXmit1

RSC

Isochronous transmit channel 1 caused the interrupt event register bit 6 (isochTx) interrupt.

0

isoXmit0

RSC

Isochronous transmit channel 0 caused the interrupt event register bit 6 (isochTx) interrupt.