17 self-id buffer pointer register, 18 self-id count register – Texas Instruments TSB12LV26 User Manual

Page 52

4–14

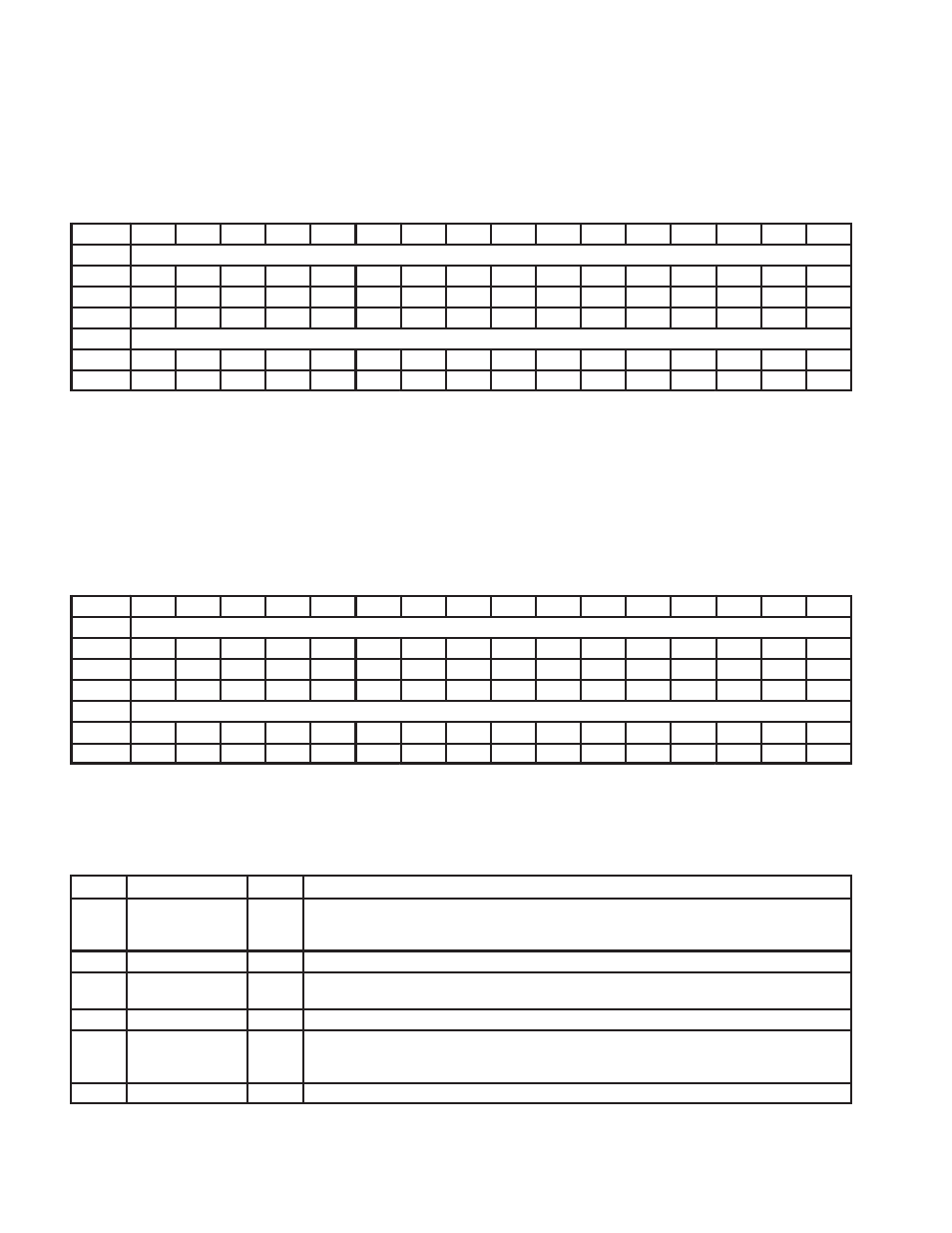

4.17 Self-ID Buffer Pointer Register

The self-ID buffer pointer register points to the 2-Kbyte aligned base address of the buffer in host memory where the

self-ID packets are stored during bus initialization. Bits 31–11 are read/write accessible. Reserved bits 10–0 are

read-only and return 0s when read.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Self-ID buffer pointer

Type

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Self-ID buffer pointer

Type

R/W

R/W

R/W

R/W

R/W

R

R

R

R

R

R

R

R

R

R

R

Default

X

X

X

X

X

0

0

0

0

0

0

0

0

0

0

0

Register:

Self ID-buffer pointer

Type:

Read/Write, Read-only

Offset:

64h

Default:

XXXX XX00h

4.18 Self-ID Count Register

The self-ID count register keeps a count of the number of times the bus self-ID process has occurred, flags self-ID

packet errors, and keeps a count of the self-ID data in the self-ID buffer. See Table 4–11 for a complete description

of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Self-ID count

Type

RU

R

R

R

R

R

R

R

RU

RU

RU

RU

RU

RU

RU

RU

Default

X

0

0

0

0

0

0

0

X

X

X

X

X

X

X

X

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Self-ID count

Type

R

R

R

R

R

RU

RU

RU

RU

RU

RU

RU

RU

RU

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Register:

Self-ID count

Type:

Read/Update, Read-only

Offset:

68h

Default:

X0XX 0000h

Table 4–11. Self-ID Count Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31

selfIDError

RU

When this bit is 1, an error was detected during the most recent self-ID packet reception. The con-

tents of the self-ID buffer are undefined. This bit is cleared after a self-ID reception in which no errors

are detected. Note that an error can be a hardware error or a host bus write error.

30–24

RSVD

R

Reserved. Bits 30–24 return 0s when read.

23–16

selfIDGeneration

RU

The value in this field increments each time a bus reset is detected. This field rolls over to 0 after

reaching 255.

15–11

RSVD

R

Reserved. Bits 15–11 return 0s when read.

10–2

selfIDSize

RU

This field indicates the number of quadlets that have been written into the self-ID buffer for the current

bits 23–16 (selfIDGeneration field). This includes the header quadlet and the self-ID data. This field is

cleared to 0 when the self-ID reception begins.

1–0

RSVD

R

Reserved. Bits 1–0 return 0s when read.