Texas Instruments MSP50C614 User Manual

Page 50

Memory Organization: RAM and ROM

2-20

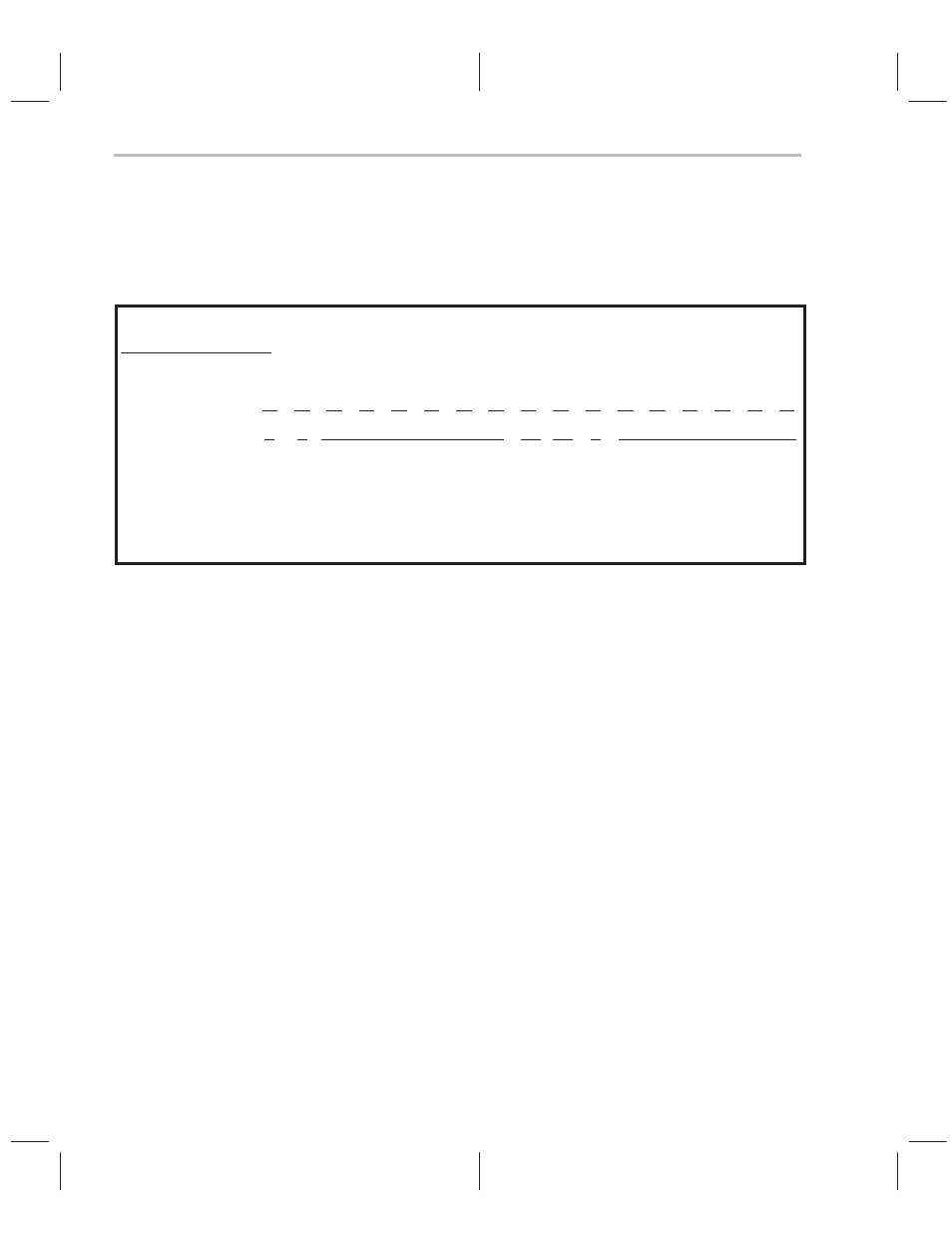

The protection modes are implemented on the C614 as follows. Within the

ROM is a dedicated storage for the block protection word (address 0x7FFE).

The block protection word is divided into two 6-bit fields and two single-bit

fields. The remainder of the 17-bit word is broken into three single-bit fields

which are reserved for future use.

ROM

Block Protection Word

address 0x7FFE

(17-bit wide location)

WRITE only

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

R

R

TM

TM

TM TM TM TM

GP BP

R

FM FM FM FM FM FM

05

04

03

02

01

00

05

04

03

02

01

00

TM : True Protection Marker (N

TM

)

GP : Global Protection (0 value protects)

FM : False Protection Marker (N

FM

)

BP : Block Protection (0 value protects)

R : Reserved for future use (must be 1)

1 : Default value of cells on erasure

The two 6-bit fields are designated as the true protection marker, (TM5 through

TM0) and the false protection marker, (FM5 through FM0). When setting up

a partition for partial ROM protection, the address of the partition must be spe-

cified as: