Texas Instruments MSP50C614 User Manual

Page 134

Instruction Classification

4-42

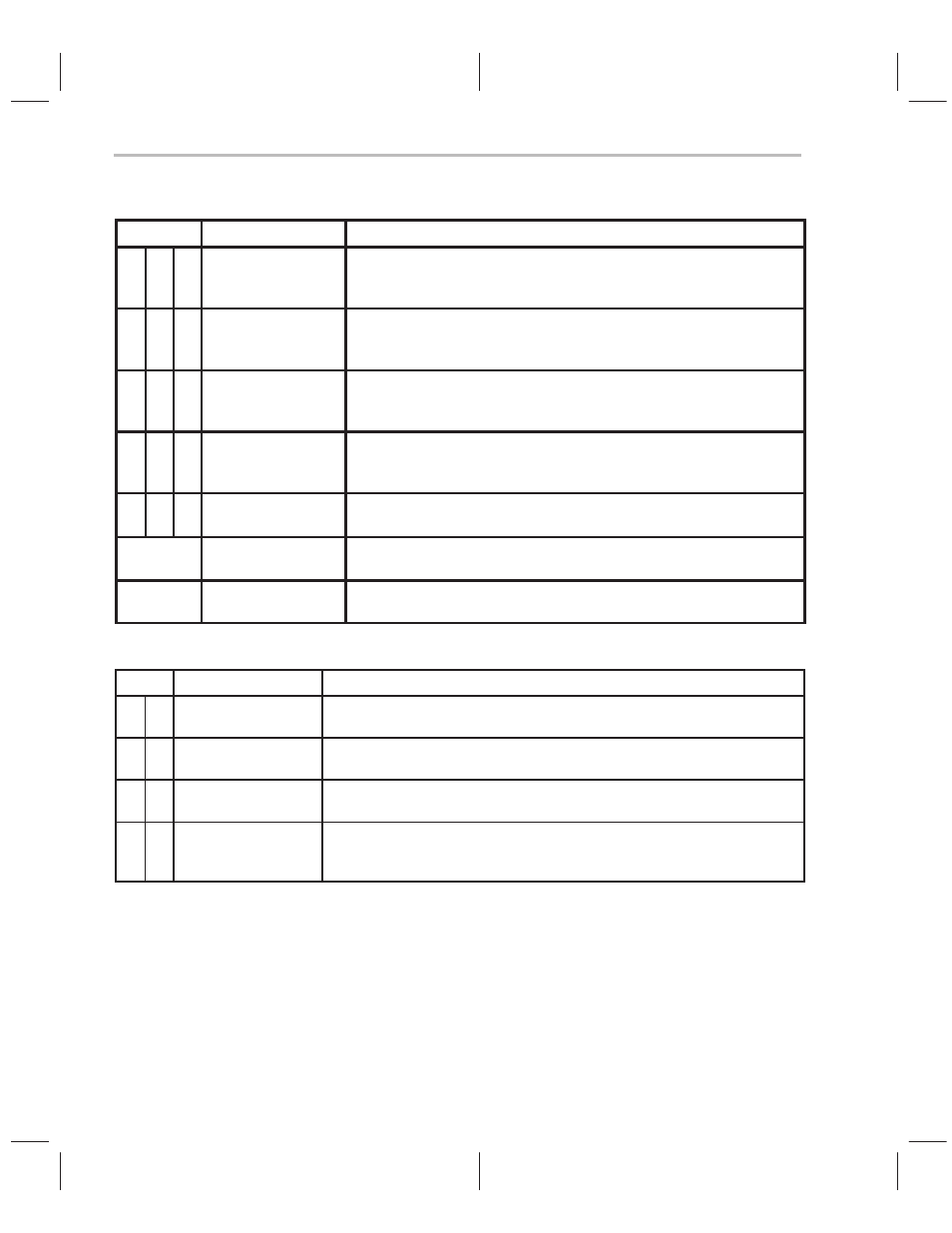

Table 4–33. Class 8a Instruction Description

C8a

Mnemonic

Description

0

0

0

MOV TF

n, {flagadrs}

Load flag bit (17

th

bit) from data memory referred by flag addressing mode

{

flagadrs} to either TF1 or TF2 in status register. Load with inverted value if

Not =1.

0

1

0

OR TF

n, {flagadrs}

Logically OR either TF1 or TF2 with flag bit (17

th

bit) from data memory

referred by flag addressing mode {

flagadrs} (or inverted value if N=1)

addressed by the instruction and store back to TF1 or TF2 respectively.

1

0

0

AND TF

n, {flagadrs}

Logically AND either TF1 or TF2 with flag bit (17

th

bit) from data memory

referred by flag addressing mode {

flagadrs} (or inverted value if Not =1)

addressed by the instruction and store back to TF1 or TF2 respectively.

1

1

0

XOR TF

n, {flagadrs}

Logically exclusive OR either TF1 or TF2 with flag bit (17

th

bit) from data

memory in {

flagadrs} if Not =1(or inverted value if Not =0) addressed by the

instruction and store back to TF1 or TF2 respectively.

0

0

1

MOV {

flagadrs}, TFn

Store TF1 or TF2 to flag bit (17

th

bit) from data memory referred by flag

addressing mode {

flagadrs}.

Table 4–32

RFLAG {

flagadrs}

Reset flag bit (17

th

bit) from data memory referred by flag addressing mode

{

flagadrs}.to 0

Table 4–32

SFLAG {

flagadrs}

Set flag bit (17

th

bit) from data memory referred by flag addressing mode

{

flagadrs}.to 1

Table 4–34. Class 8b Instruction Description

C8b

Mnemonic

Description

0

0

MOV TF

n, {cc} [, Rx]

Load a logic value of the tested condition to one of the test flag bits in

status register (TF1 or TF2).

0

1

OR TF

n, {cc} [, Rx]

Logically modify one of the two test flags in status register (TF1 or TF2) by

ORing it with the status condition specified.

1

0

AND TF

n, {cc} [, Rx]

Logically modify one of the two test flags in status register (TF1 or TF2) by

ANDing it with the status condition specified.

1

1

XOR TF

n, {cc} [, Rx]

Logically modify one of the two test flags in status register (TF1 or TF2) by

EXCLUSIVE ORing it with the status condition specified. For this instruction

the polarity of

Not is inverted (Not =1 for XOR, Not=0 for XNOR).

4.4.9

Class 9 Instructions: Miscellaneous

This instruction class includes all the remaining instructions that do not fit in

the previous classes. Some instructions have byte wide operand fields and

others have no operands. One subclass is a set of instructions that provide

specific DSP functions (FIR filters). Another subclass provides some

hardware/ software loop capability. Ten instructions provide the means to set

or reset five different status mode bits independently.