15 instruction set encoding – Texas Instruments MSP50C614 User Manual

Page 279

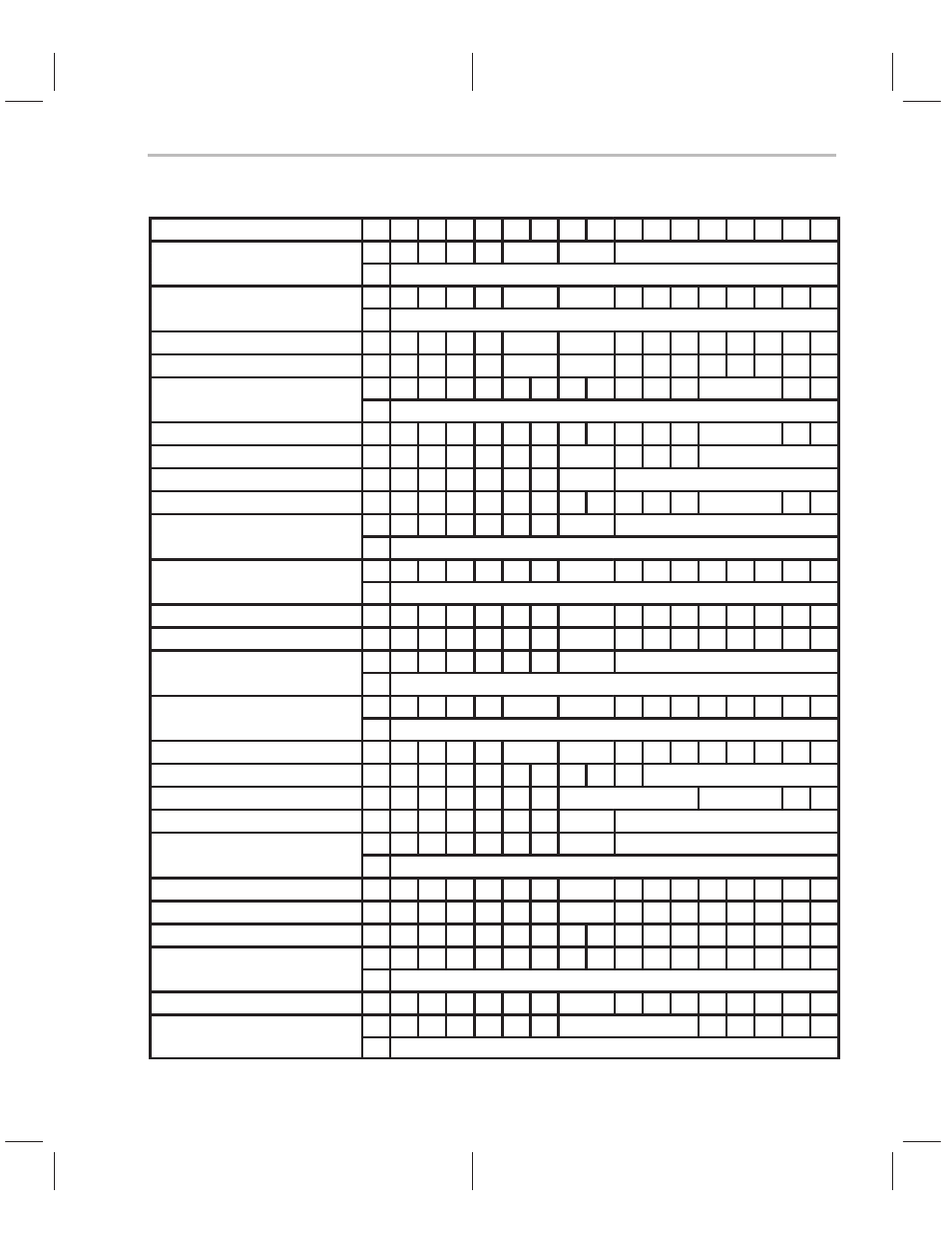

Instruction Set Encoding

4-187

Assembly Language Instructions

4.15 Instruction Set Encoding

Instructions

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ADD A

n[~], An, {adrs} [, next A]

1

1

1

0

~A

next A

A

n

adrs

x

dma16 (for direct) or offset16 (long relative) [see section 4.13]

ADD A

n[~], An[~], imm16 [, next A]

1

1

1

0

0

next A

A

n

0

0

0

0

0

1

A~

~A

x

imm16

ADD A

n[~], An[~], PH [, next A]

1

1

1

0

0

next A

A

n

0

1

1

0

1

0

A~

~A

ADD A

n[~], An~, An [, next A]

1

1

1

0

0

next A

A

n

0

0

1

0

1

0

A~

~A

ADD R

x, imm16

1

1

1

1

1

1

1

0

0

0

0

0

R

x

0

0

x

imm16

ADD R

x, R5

1

1

1

1

1

1

1

0

0

1

0

0

R

x

0

0

ADD AP

n, imm5

1

1

1

1

1

0

1

AP

n

0

1

0

imm5

ADDB A

n, imm5

1

0

1

0

0

0

0

A

n

imm8

ADDB R

x, imm8

1

0

1

1

0

0

k4

k3

k2

k7

k6

k5

R

x

k1

k0

ADDS A

n[~], An, {adrs}

0

0

0

0

~A

1

1

A

n

adrs

x

dma16 (for direct) or offset16 (long relative) [see section 4.13]

ADDS A

n[~], An[~], pma16

1

1

1

0

0

1

1

A

n

0

0

0

0

0

1

A~

~A

x

pma16

ADDS A

n[~], An~, An

1

1

1

0

0

1

1

A

n

0

0

1

0

1

0

A~

~A

ADDS A

n[~], An[~], PH

1

1

1

0

0

1

1

A

n

0

1

1

0

1

0

A~

~A

AND A

n, {adrs}

0

1

0

0

0

1

0

A

n

adrs

x

dma16 (for direct) or offset16 (long relative) [see section 4.13]

AND A

n[~], An[~], imm16 [, next A]

1

1

1

0

0

next A

A

n

1

0

1

0

0

1

A~

~A

x

imm16

AND A

n[~], An~, An [, next A]

1

1

1

0

0

next A

A

n

0

1

0

1

0

0

A~

~A

AND TF

n, {flagadrs}

1

0

0

1

1

flg Not

1

0

0

flagadrs

AND TF

n, {cc} [, Rx]

1

0

0

1

0

flg Not

cc

R

x

1

0

ANDB A

n, imm8

1

0

1

0

1

0

1

A

n

imm8

ANDS A

n, {adrs}

0

1

0

0

0

1

1

A

n

adrs

x

dma16 (for direct) or offset16 (long relative) [see section 4.13]

ANDS A

n[~], An[~], pma16

1

1

1

0

0

1

1

A

n

1

0

1

0

0

1

A~

~A

ANDS A

n[~], An~, An

1

1

1

0

0

1

1

A

n

0

1

0

1

0

0

A~

~A

BEGLOOP

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

CALL

pma16

1

0

0

0

0

1

0

1

0

1

0

1

0

0

0

0

0

x

pma16

CALL *A

n

1

0

0

0

1

1

0

A

n

0

0

0

0

0

0

0

0

C

cc pma16

1

0

0

0

0

1

Not

cc

0

0

0

0

0

x

pma16