Texas Instruments MSP50C614 User Manual

Page 125

Instruction Classification

4-33

Assembly Language Instructions

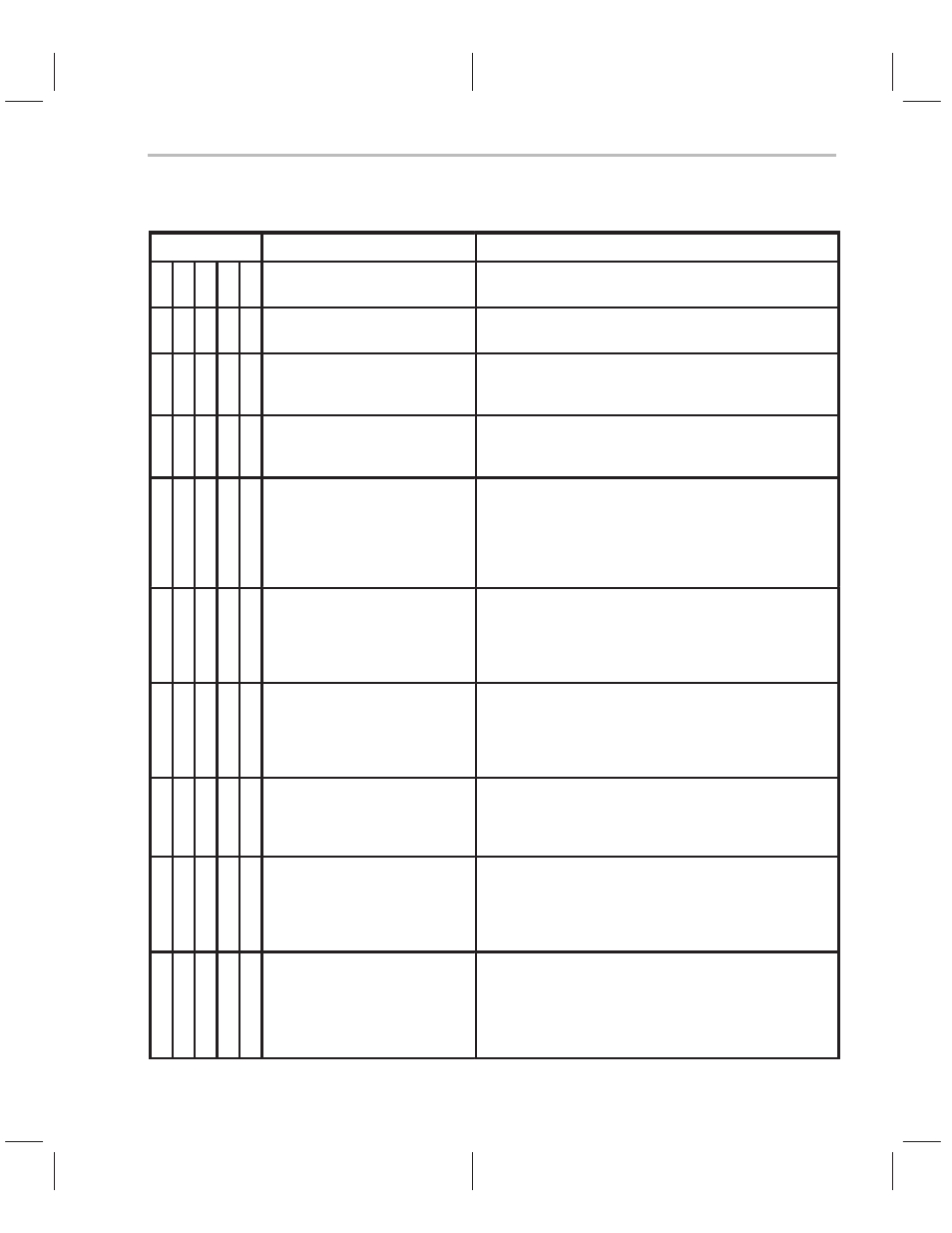

Table 4–20. Class 3 Instruction Description (Continued)

C3

Mnemonic

Description

1

0

1

0

0

MOV SV, A

n[~] [, next A]

MOVS SV, A

n[~]

Transfer accumulator(A~=0) or offset accumulator (A~=1)

to SV register. Transfer status is modified.

1

0

1

0

1

MOV PH, A

n[~] [, next A]

MOVS PH, A

n[~]

Transfer accumulator (A~=0) or offset accumulator (A~=1)

to PH register. Transfer status is modified.

1

0

1

1

0

MOV MR, A

n[~] [, next A]

MOVS MR, A

n[~]

Transfer accumulator (A~=0) or offset accumulator (A~=1)

to MR register in the signed multiplier mode (UM bit in

status register set to 0). Transfer status is modified.

1

0

1

1

1

MOVU MR, A

n[~] [, next A]

Transfer accumulator (A~=0 or 1) to MR register in the

unsigned multiplier mode(UM bit set to 1). Transfer status

is modified.

1

1

0

0

0

MULSPL A

n[~], An[~] [, next A]

MULSPLS A

n[~], An[~]

Multiply the MR register by accumulator (A~=1) or offset

accumulator (A~=0) , subtract lower 16 bits of the product

from the offset accumulator (A~=1) or accumulator

(A~=0). Store in the accumulator (~A=0) or offset

accumulator (~A=1). Latch the upper 16 bits in PH. ALU

status is modified.

1

1

0

0

1

MULAPL A

n[~], An[~] [, next A]

MULAPLS A

n[~], An[~]

Multiply MR register by accumulator (A~=1) or offset

accumulator (A~=0) , add lower 16 bits of product to offset

accumulator (A~=1) or accumulator (A~=0) and store to

accumulator (~A=0) or offset accumulator (~A=1). Latch

upper 16 bits in PH. ALU status is modified.

1

1

0

1

0

SHLTPL A

n[~], An[~][, next A]

SHLTPLS A

n[~], An[~]

Barrel shift the accumulator (A~=1 or 1) value n bits left

(SV reg). Store the upper 16 bits of the 32 bit shift result to

PH (msbs extended by XM mode bit). Transfer the lower

16 bits to accumulator (~A=0) or offset(~A=1). ALU status

is modified.

1

1

0

1

1

MULTPL A

n[~], An[~] [, next A]

MULTPLS A

n[~], An[~]

Multiply MR register by accumulator(A~=1) or offset

(A~=0), transfer lower 16 bits of product to accumulator

(~A=0) or offset accumulator(~A=1). Latch upper 16 bits of

Product to PH register. ALU status is modified.

1

1

1

0

0

SHLSPL A

n[~], An[~] [, next A]

SHLSPLS A

n[~], An[~]

Barrel shift the accumulator(A~=1) or offset accumulator

(A~=0) value n bits left (SV reg). Store the upper 16 bits to

PH. Subtract the lower 16 bits of value from offset (A~=1)

or accumulator (A~=0) and store in accumulator (~A=0) or

offset accumulator (~A=1). ALU status is modified.

1

1

1

0

1

SHLAPL A

n[~], An[~] [, next A]

SHLAPLS A

n[~], An[~]

Barrel shift the accumulator(A~=1) or offset accumulator

(A~=0) value n bits left (SV reg). Store the upper 16 bits to

PH. Add the lower 16 bits of value to offset accumulator

(A~=1) or accumulator (A~=0) and store in accumulator

(~A=0) or offset accumulator(~A=1). ALU status is

modified.