7 begloop begin loop – Texas Instruments MSP50C614 User Manual

Page 176

Individual Instruction Descriptions

4-84

4.14.7 BEGLOOP

Begin Loop

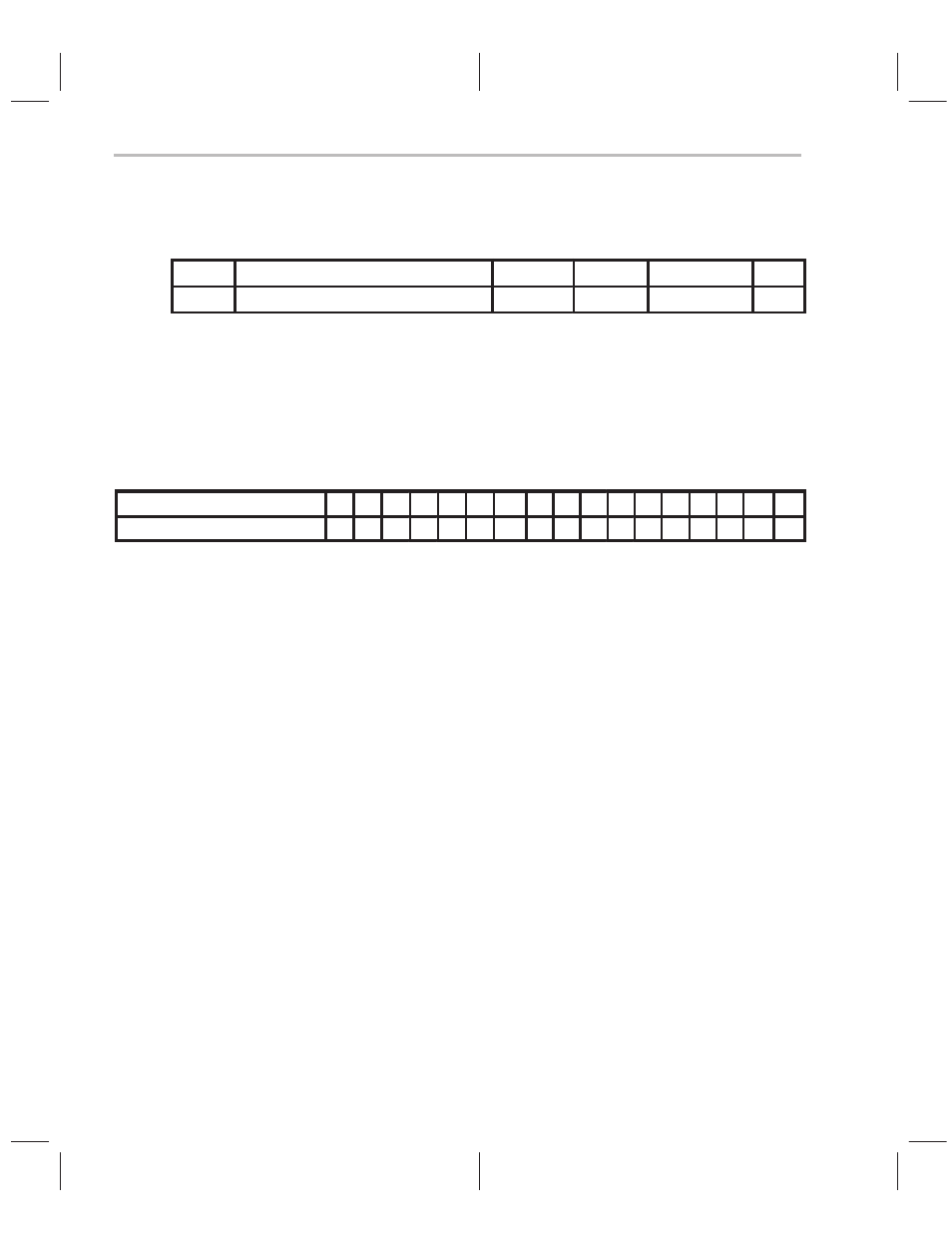

Syntax

[label]

name

Clock,

clk

Word,

w

With RPT,

clk

Class

BEGLOOP

†

1

1

N/R

9d

† Loop must end with ENDLOOP.

Execution

Save next instruction address (PC + 1)

(

mask interrupts)

PC

⇐

PC + 1

Flags Affected

none

Opcode

Instructions

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

BEGLOOP

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

Description

This instruction saves the next sequential address in a shadow register and

masks interrupts. Interrupts occurring during execution of this and following

instructions are actually queued until the loop is complete (see ENDLOOP).

The loop executes N number of times. Thus, N – 2, should be loaded in R4

in order to loop N times.

BEGLOOP and ENDLOOP block has following restrictions:

-

No CALL instructions can be used.

-

All maskable interrupts are queued.

-

BEGLOOP/ENDLOOP block cannot be nested.

See Also

ENDLOOP

Example 4.14.7.1

MOV R4, count – 2 ;init R4 with loop count

BEGLOOP

ADD A0, A0~, A0

;add A0~ to A0 (count) times

ENDLOOP

Initialize R4 with the loop count value minus 2 to repeat the loop for count times. Execute the ADD A0,

A0~, A0 instruction until R4 is negative. R4 is decremented each time ENDLOOP is encountered. When

R4 is negative, ENDLOOP becomes a NOP and execution continues with the next instruction after

ENDLOOP.