Texas Instruments MSP50C614 User Manual

Page 129

Instruction Classification

4-37

Assembly Language Instructions

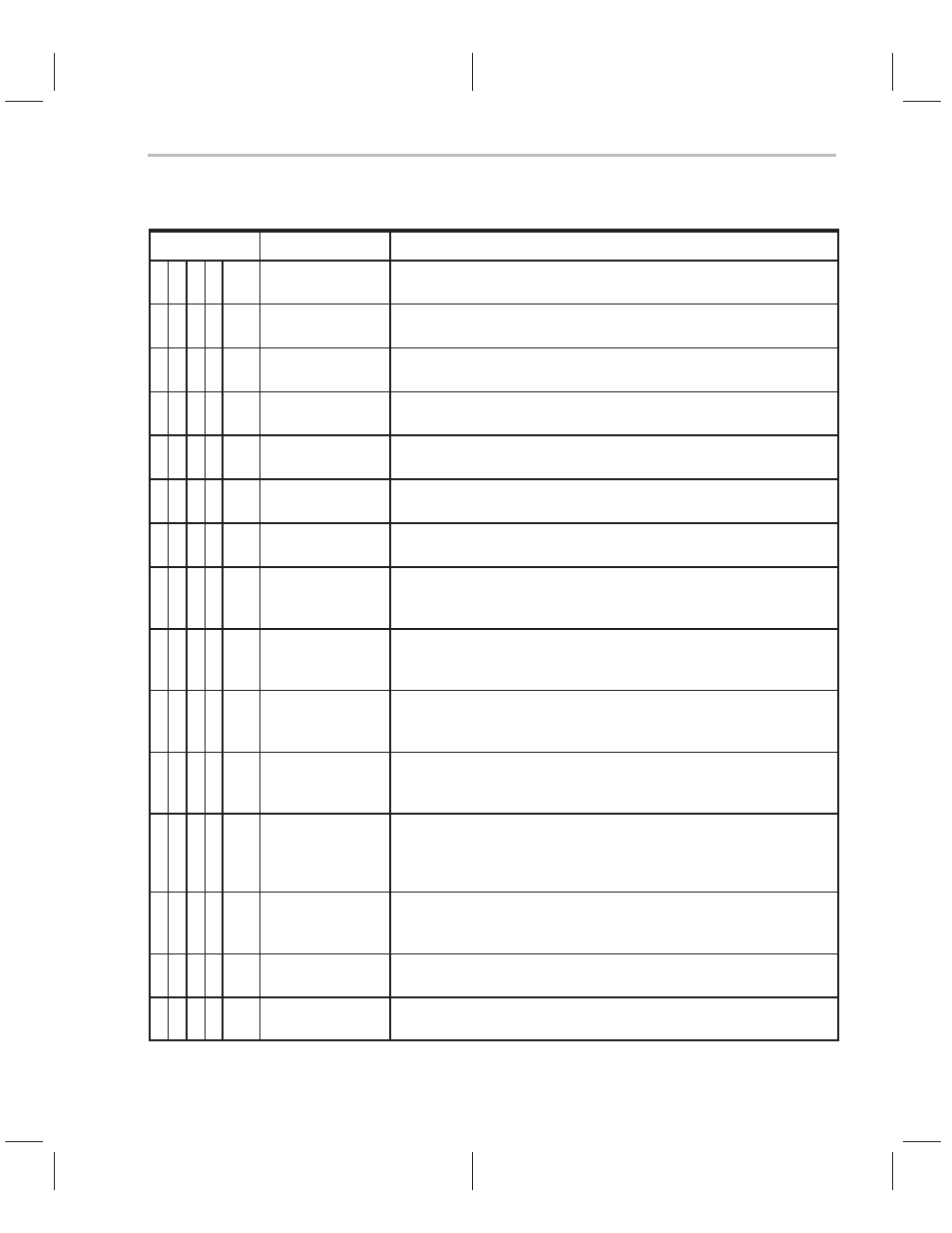

Table 4–27. Class 5 Instruction Description (Continued)

C5

Mnemonic

Description

0 1 0 1

1

MOV {

adrs}, TOS

Store the contents of the top of stack (TOS) register to the data memory

location referred by addressing mode {

adrs}. Transfer status is modified.

0 1 1 0

0

STAG {

adrs}

Store 1 to the 17

th

bit of data memory location referred by {

adrs}. Set the

tag bit.

0 1 1 0

1

RTAG {

adrs}

Store 0 to the 17

th

bit of data memory location referred by {

adrs}. Clear

the tag bit.

0 1 1 1

n–1

MOVT {

adrs}, TFn

Store TF1 bit if

n=1, TF2 bit if n=0 status bit to 17

th

bit of data memory

location referred by addressing mode {

adrs}.

1 0 0 0

0

MOV SV, {

adrs}

4

Load shift value (SV) register with contents of the location referred by ad-

dressing mode {

adrs}. Transfer status is modified.

1 0 0 0

1

MOV PH, {

adrs}

Load Product High (PH) register with content of data memory location

value referred by addressing mode {

adrs}. Transfer is status modified.

1 0 0 1

0

MOV TOS, {

adrs}

Load top of stack (TOS) register with content of data memory location

referred by addressing mode {

adrs}.

1 0 0 1

1

MOV STR, {

adrs}

8

Load String (STR) register with content of data memory location referred

by addressing mode {

adrs}. Only the lower 8 bits are loaded. Transfer

status modified.

1 0 1 n

n

MOV AP

n, {adrs}

Load lower 5 bits with content of data memory location referred by

addressing mode {

adrs} to accumulator pointer (AP) register n. Transfer

status is modified (16 bit value).

1 1 0 0

0

MOV MR, {

adrs}

Load Multiplier (MR) register with content of data memory location

referred by addressing mode {

adrs} and set the multiplier signed mode

(UM=0 in STAT register). Transfer status is modified.

1 1 0 0

1

MOVU MR, {

adrs}

Load Multiplier (MR) register with content of data memory location

referred by addressing mode {

adrs} and set the multiplier unsigned mode

(UM=1 in STAT register). Transfer status is modified.

1 1 0 1

0

MULR {

adrs}

Multiply MR register by content of data memory location referred by

addressing mode {

adrs}, add 0x00008000 to the 32 bit product to

produce a rounding on the upper 16 bits. Store the upper rounded 16 bits

to the PH register. No status change.

1 1 0 1

1

MUL {

adrs}

Multiply MR register by content of data memory location referred by

addressing mode {

adrs} and store the most significant 16 bits of product

into the PH register. No status change.

1 1 1 0

0

RET

†

Return from subroutine. Load data memory location value addressed by

R7 (STACK) to program counter.

1 1 1 0

1

IRET

†

Return from interrupt routine. Load data memory location value ad-

dressed by R7 (STACK) to program counter.

† The entire 17 bit is encoded. See Table 4–26.