Texas Instruments MSP50C614 User Manual

Page 388

Mechanical Information

7-6

The pin assignments for the 120-pin PGA are outlined in the following table.

(Refer to Section 1.6 for more information on the signal functions.)

Figure 7–3 provides a cross-reference between the C614 (die) pad numbers

and the P614’s PGA package leads.

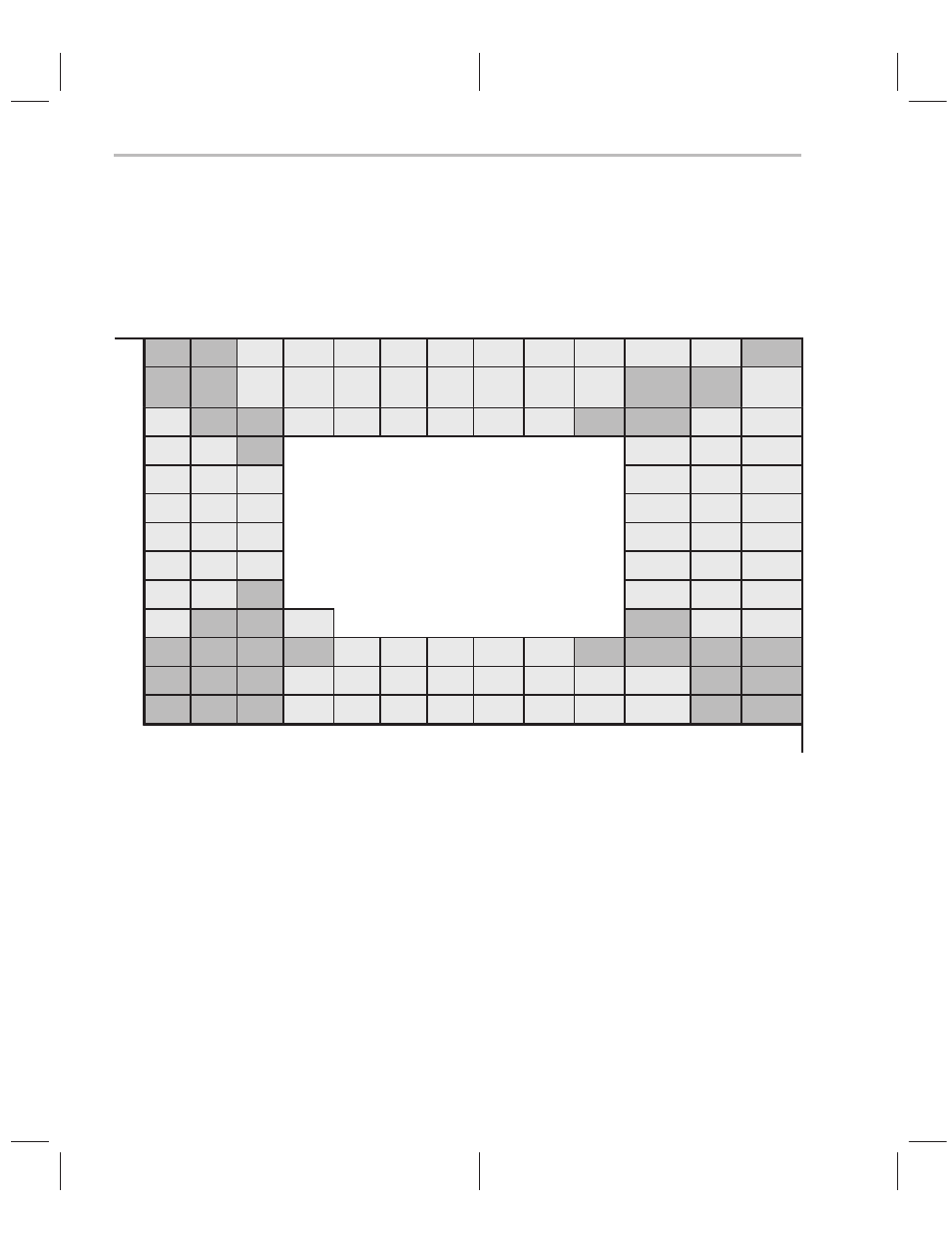

Figure 7–3. 120 Pin Grid Array (PGA) Package Leads, P614

N

nc

nc

†VDD

PF7

PF5

PF2

VPP

PG15

PG12

PG10

VSS

VDD

nc

M

nc

nc

DAC

M

DACP

PF6

PF3

PF1

PG14

PG11

PG8

nc

nc

PG7

L

PD0

nc

nc

†VSS

VDD

PF4

PF0

PG13

PG9

nc

nc

PG5

PG4

K

PD3

PD1

nc

PG6

PG3

PG1

J

PD5

PD4

PD2

PG2

PG0

scanout

H

VDD

PD7

PD6

pgmpuls

SYNC

scanclk

G

VSS

PC1

PC0

(bottom view)

RESET

scanin

PE7

F

PC2

PC3

PC4

PE4

PE5

PE6

E

PC5

PC6

nc

PE0

PE2

PE3

D

PC7

nc

nc

extra

nc

VSS

PE1

C

nc

nc

nc

nc

PB1

PB5

VSS

PA3

PA7

nc

nc

nc

nc

B

nc

nc

nc

PB0

PB3

PB6

PA0

PA2

PA5

PLL

OSCOUT

nc

nc

A

nc

nc

nc

PB2

PB4

PB7

VDD

PA1

PA4

PA6

OSCIN

nc

nc

1

2

3

4

5

6

7

8

9

10

11

12

13

† It is important to provide a separate decoupling capacitor for the VDD, VSS pair which services the DAC. These pins are PGA

numbers

N3 and L4, respectively. The relatively high current demands of the digital-to-analog circuitry make this a requirement.

Refer to section 6.1 for details.

The following table provides a cross-reference between the C614 (die) pad

numbers and the P614’s PGA package leads.