84 xor logical xor – Texas Instruments MSP50C614 User Manual

Page 273

Individual Instruction Descriptions

4-181

Assembly Language Instructions

4.14.84

XOR

Logical XOR

Syntax

[label]

name

dest, src, src1 [, mod]

Clock,

clk

Word,

w

With RPT,

clk

Class

XOR

A

n, {adrs}

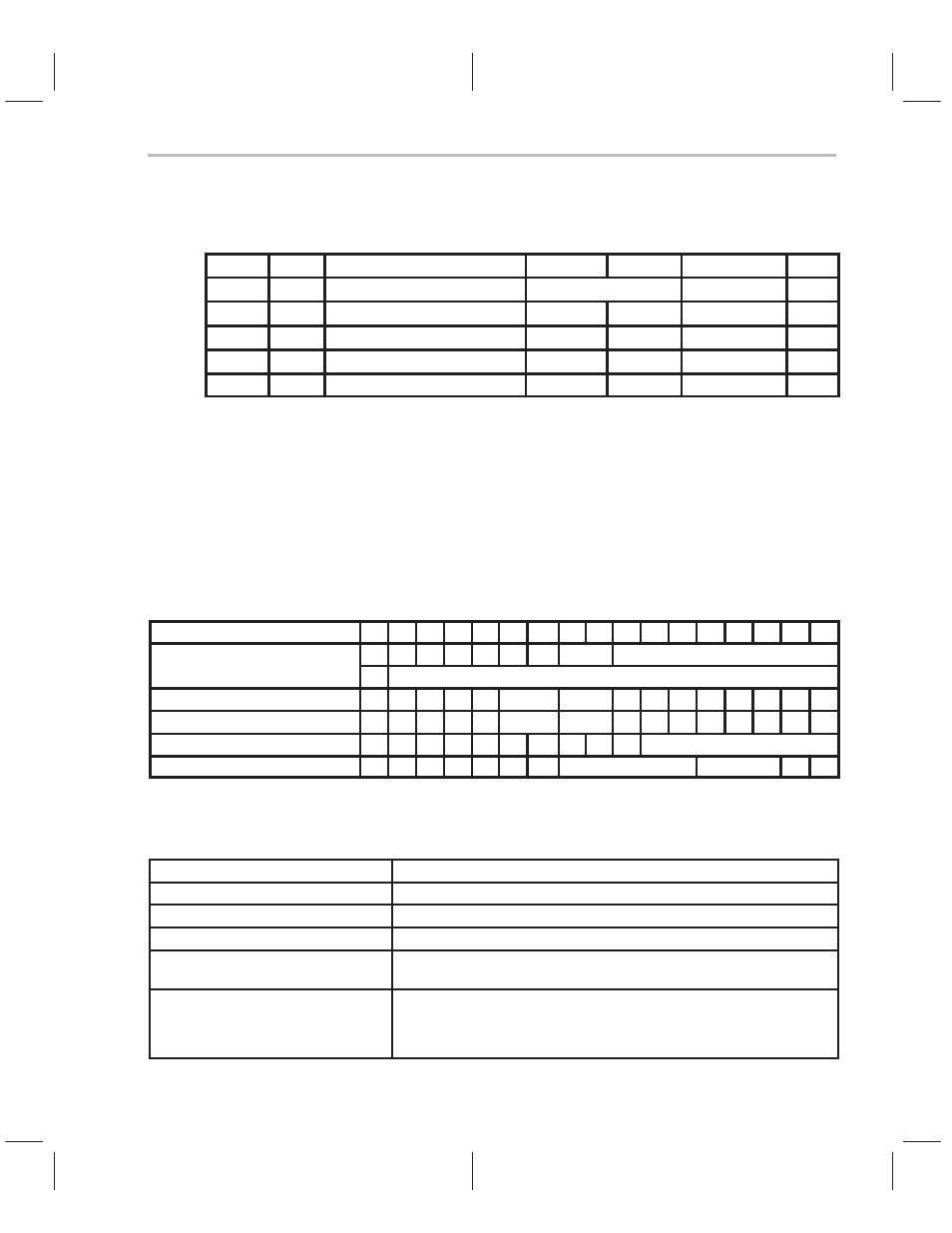

Table 4–46

Table 4–46

1a

XOR

A

n[~], An[~], imm16 [, next A]

2

2

N/R

2b

XOR

A

n[~], An~, An [, next A]

1

1

n

R

+3

3

XOR

TF

n, {flagadrs}

1

1

N/R

8a

XOR

TF

n, {cc} [, Rx]

1

1

n

R

+3

8b

Execution

[premodify AP if

mod specified]

dest

⇐

dest XOR src

(for two operands)

dest

⇐

src1 XOR src

(for three operands)

PC

⇐

PC +

w

Flags Affected

dest is An:

OF, SF, ZF, CF are set accordingly

dest is TFn:

TF

n bits in STAT register are set accordingly

src is {adrs}:

TAG bit is set accordingly

src is {flagadrs}:

TAG bit is set accordingly

Opcode

Instructions

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

XOR A

n, {adrs}

0

1

0

0

1

0

0

A

n

adrs

x

dma16 (for direct) or offset16 (long relative) [see section 4.13]

XOR A

n[~], An[~], imm16 [, next A]

1

1

1

0

0

next A

A

n

1

1

0

0

0

1

A~

~A

XOR A

n[~], An~, An [, next A]

1

1

1

0

0

next A

A

n

0

1

0

0

0

0

A~

~A

XOR TF

n, {flagadrs}

1

0

0

1

1

fig

Not

1

1

0

flagadrs

XOR TF

n, {cc} [, Rx]

1

0

0

1

0

fig

Not

cc

R

x

1

1

Description

Bitwise logical XOR of

src and dest. Result is stored in dest. If three operands

are specified, then logical XOR

src and src1, store the result in dest. Pre-

modification of accumulator pointers is allowed with some operand types.

Syntax

Description

XOR A

n, {adrs}

XOR RAM word to A

n

XOR A

n[~], An[~], imm16 [, next A]

XOR immediate word to A

n[~], store result in An[~]

XOR A

n[~], An~, An [, next A]

XOR A

n word to An~ word, store result in An[~]

XOR TF

n, {flagadrs}

XOR TF

n (either TF1 or TF2) with memory tag, store result in TFn bit in

STAT

XOR TF

n, {cc} [, Rx]

XOR test condition with TF

n (either TF1 or TF2) bit in STAT register. Rx

must be provided if

cc is one of {RZP, RNZP, RLZP, RNLZP} to check if

the selected R

x is zero or negative. Rx should not be provided for other

conditionals.