Appendix a : protocol configuration commands – Welltech SPCI2S Intel NetStructure SS7 Boards User Manual

Page 91

SS7 Programmer’s Manual for SPCI2, SPCI4 and CPM8 Issue 2

Page 91

APPENDIX A : PROTOCOL CONFIGURATION COMMANDS

This appendix describes the commands and parameters used in the protocol configuration file

config.txt. These are used by the s7_mgt utility to perform single-shot configuration of the protocol

stack at startup.

A1 Physical Interface Parameters

A1.1 SEPTELCP_BOARD / SEPTELPCI_BOARD Command

Syntax: SEPTELCP_BOARD

SEPTELPCI_BOARD

Example: SEPTELCP_BOARD 0 0x0043 ss7.dc3 ISUP-L

Commands to configure a SPCI2S and SPCI4 boards (SEPTELPCI_BOARD) and CPM8 boards

(SEPTELCP_BOARD) in the system.

The logical id of the board within the system in the range 0 .. 15.

A 16 bit value that provides additional level 1 configuration for the board. The meaning of each bit

may vary with different board types. The bits in the flags field are used as follows:

Bit 0 controls the reference source used for on-board clocks when acting as CT bus Primary

Master. If set to 1 then the clock will be recovered from one of the line interfaces. If set to zero

then the on-board clock oscillator will be used.

Bit 1 is reserved for future use and should always be set to 1.

Bit 6 and 7 together select the initial clocking mode for the CT bus as shown in the following table.

The clocking mode can subsequently modified dynamically using the MVD_MSG_CNFCLOCK

message:

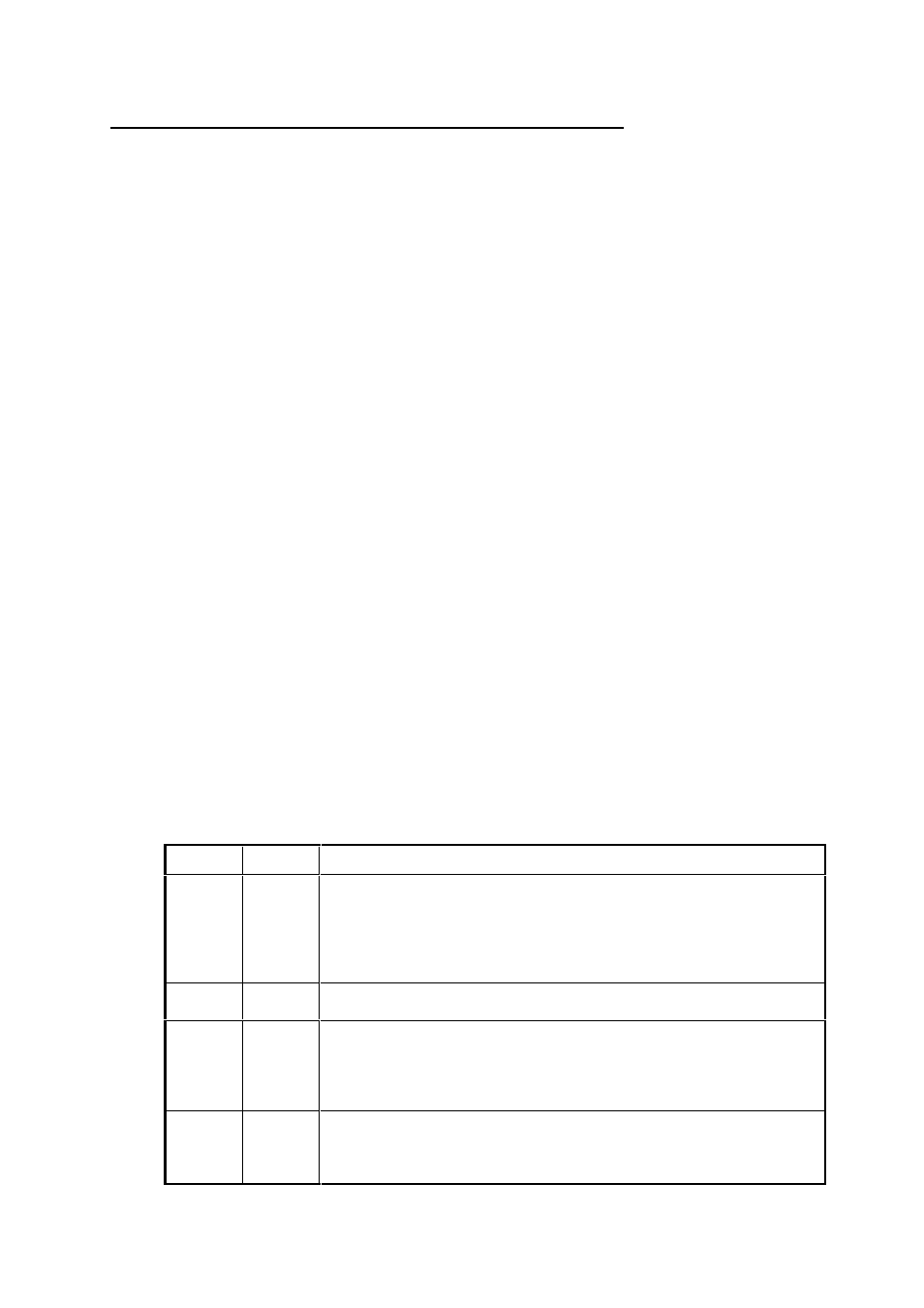

Bit 7

Bit 6

CT bus clocking mode

0 0

The CT bus interface is disabled - In this mode the card is

electrically isolated from the other cards using the CT bus. The CT

bus connection commands may still be used, but the connections

made will only be visible to this card. When using this mode, the on-

board clocks will be synchronised to the source selected by bit 0 of

this flags parameter.

0 1

Primary Master, Clock set A - The board will drive CT bus clock set

A using the clock source selected by bit 0 of this flags parameter.

1 0

Secondary Master, Clock set B - The board is configured to drive

clock set B in Secondary Master mode. It will automatically switch to

become Primary Master if the board driving clock set A fails. While

acting as Secondary Master the on-board clocks will be synchronised

to the CT bus clock set A.

1 1

Slave, initially using Clock set A – The board uses the CT bus

clocks, which must be generated by another board on the CT bus.

Initially the board will recover from clock set A, though will switch over

automatically to recover from clock set B should set A fail