Power measurement, Power measurement –51 – Altera Cyclone V SoC Development Board User Manual

Page 59

Chapter 2: Board Components

2–51

Power Supply

November 2013

Altera Corporation

Cyclone V SoC Development Board

Reference Manual

Power Measurement

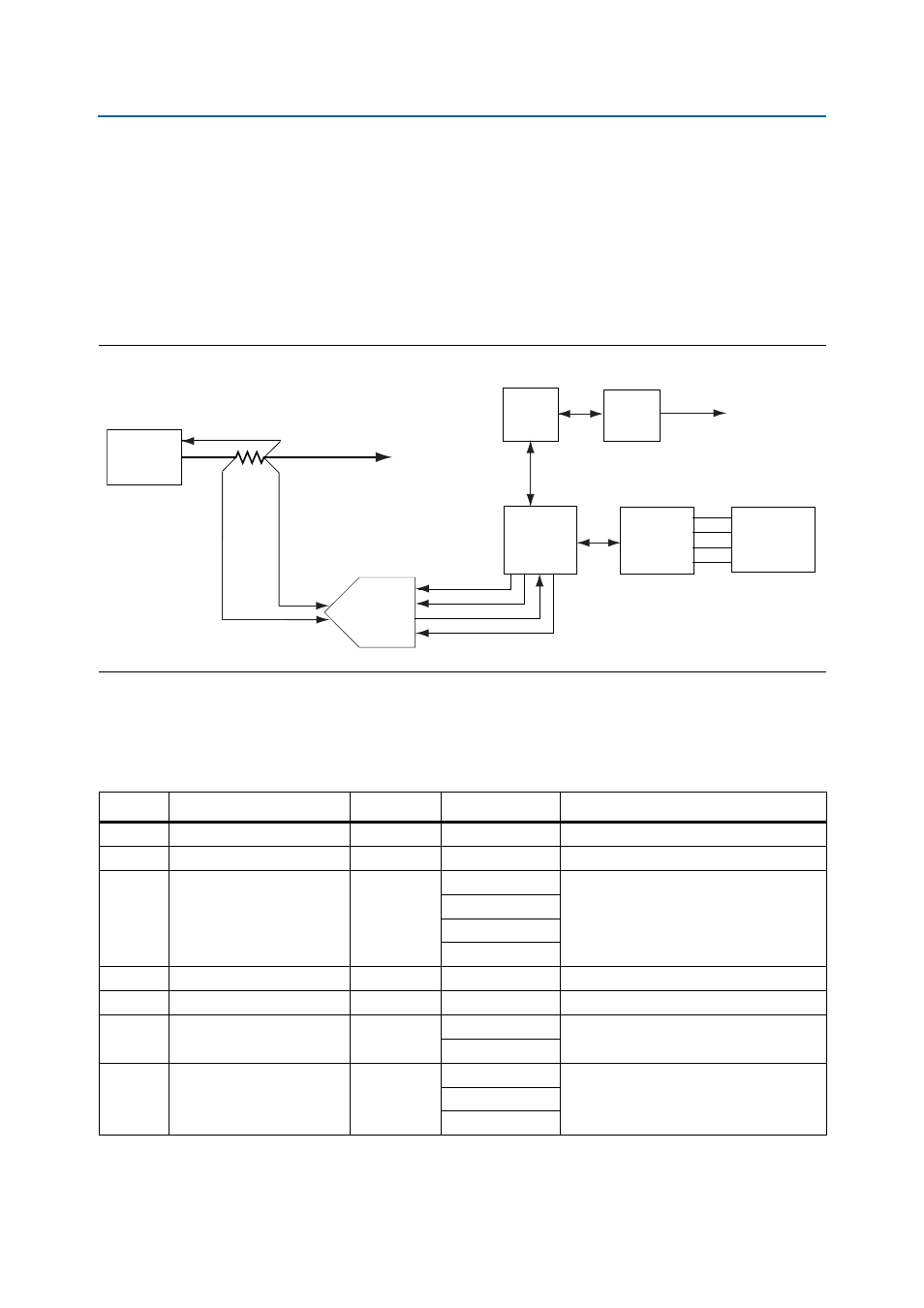

There are seven power supply rails that have on-board current sense capabilities

using 16-bit differential ADC devices. Precision sense resistors split the ADC devices

and rails from the primary supply plane for the ADC to measure current. A SPI bus

connects these ADC devices to the FPGA, HPS, and MAX V CPLD 5M2210 System

Controller.

shows the block diagram for the power measurement circuitry.

lists the targeted rails. The schematic signal name column specifies the

name of the rail being measured while the device pin column specifies the devices

attached to the rail.

Figure 2–11. Power Measurement Circuit

SCK

SPI Bus

DSI

DSO

CSn

8 Ch.

Power Supply Load #0-6

R

SENSE

MAX V CPLD

5M2210

System

Controller

Cyclone V

SoC

To User PC

JTAG Chain

Feedback

14-pin

2x16

Character

LCD

E

RW

RS

D(0:7)

Supply

#0-6

EPM570

USB

PHY

Embedded

USB-Blaster II

Table 2–40. Power Measurement Rails

Channel

Schematic Signal Name

Voltage (V)

Device Pin

Description

0

1.1V_HPS

1.1

VCC_HPS

HPS core power

1

1.5V_HPS

1.5

VCCIO6A_HPS

I/O and DDR3 devices

2

3.3V_HPS

3.3

VCCIO7A_HPS

I/O and HPS peripheral devices

VCCIO7B_HPS

VCCIO7C_HPS

VCCIO7D_HPS

3

2.5V_HPS

2.5

VCCPD6A6B_HPS I/O, HPS internal and peripheral devices

4

1.1V_VCC

1.1

VCC

FPGA core power, transceiver, and clock

5

1.5V_FPGA

1.5

VCCIO3B

I/O and DDR3 devices

VCCIO4A

6

2.5V_FPGA

2.5

VCCIO5A

I/O, FPGA internal and peripheral devices

VCCIO5B

VCCIO8A