Altera Cyclone V SoC Development Board User Manual

Page 35

Chapter 2: Board Components

2–27

Components and Interfaces

November 2013

Altera Corporation

Cyclone V SoC Development Board

Reference Manual

lists the Ethernet PHY interface pin assignments.

The Micrel KSZ9021RN PHY uses a multi-level POR bootstrap encoding scheme to

allow a small set of I/O pins (7) to set up a very large number of default settings

within the device. The related I/O pins have integrated pull-up or pull-down resistors

to configure the device.

lists the level encoding scheme.

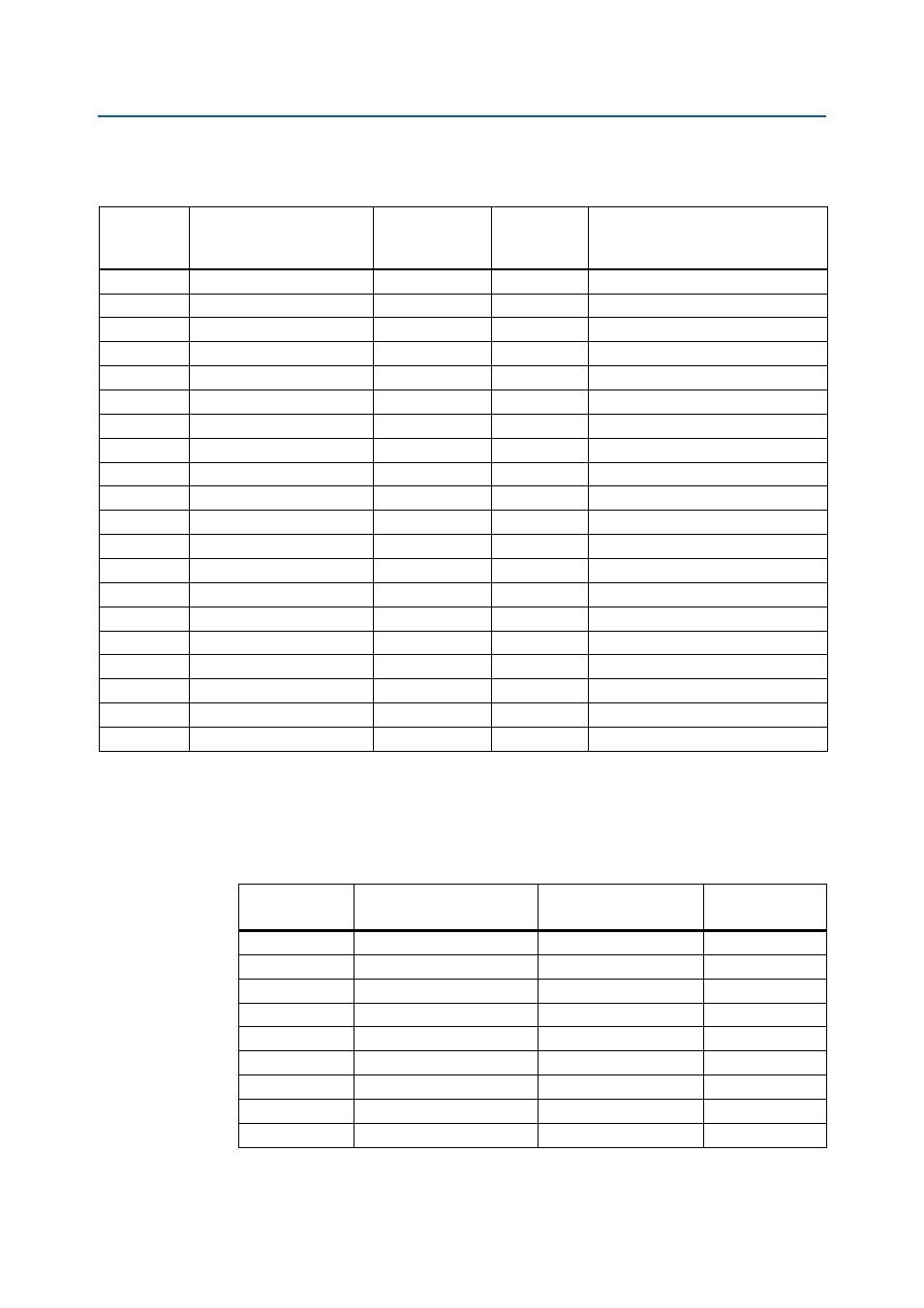

Table 2–19. Ethernet PHY Pin Assignments, Signal Names and Functions

Board

Reference

(U11)

Schematic Signal Name

Cyclone V SoC

Pin Number

I/O Standard

Description

41

CLK125_NDO_LED_MODE

—

—

Clock out 125-MHz LED mode

24

ENET_HPS_GTX_CLK

H19

3.3-V CMOS

125-MHz RGMII transmit clock

38

ENET_HPS_INTN

C19

3.3-V CMOS

Management bus interrupt

17

ENET_HPS_LED1_LINK

—

3.3-V CMOS

Receive data active LED

15

ENET_HPS_LED2_LINK

—

3.3-V CMOS

Transmit data active LED

36

ENET_HPS_MDC

B21

3.3-V CMOS

Management bus data clock

37

ENET_HPS_MDIO

E21

3.3-V CMOS

Management bus data

42

ENET_HPS_RESETN

—

3.3-V CMOS

Device reset

48

ENET_HPS_RSET

—

3.3-V CMOS

Device interrupt

35

ENET_HPS_RX_CLK

G20

3.3-V CMOS

RGMII receive clock

33

ENET_HPS_RX_DV

K17

3.3-V CMOS

RGMII receive data valid

32

ENET_HPS_RXD0

A21

3.3-V CMOS

RGMII receive data bus

31

ENET_HPS_RXD1

B20

3.3-V CMOS

RGMII receive data bus

28

ENET_HPS_RXD2

B18

3.3-V CMOS

RGMII receive data bus

27

ENET_HPS_RXD3

D21

3.3-V CMOS

RGMII receive data bus

25

ENET_HPS_TX_EN

A20

3.3-V CMOS

RGMII transmit enable

19

ENET_HPS_TXD0

F20

3.3-V CMOS

RGMII transmit data bus

20

ENET_HPS_TXD1

J19

3.3-V CMOS

RGMII transmit data bus

21

ENET_HPS_TXD2

F21

3.3-V CMOS

RGMII transmit data bus

22

ENET_HPS_TXD3

F19

3.3-V CMOS

RGMII transmit data bus

Table 2–20. Ethernet PHY (HPS) Bootstrap Encoding Scheme

Board Reference

(U11)

Schematic Signal Name

Description

Strapping Option

17

ENET_HPS_LED1_LINK

PHY address bit 0

Pulled low

15

ENET_HPS_LED2_LINK

PHY address bit 1

Pulled low

32

ENET_HPS_RXD0

Mode 0

Pulled high

31

ENET_HPS_RXD1

Mode 1

Pulled high

28

ENET_HPS_RXD2

Mode 2

Pulled high

27

ENET_HPS_RXD3

Mode 3

Pulled high

35

ENET_HPS_RX_CLK

PHY address bit 2

Pulled high

33

ENET_HPS_RX_DV

Clock enable

Pulled low

41

CLK125_NDO_LED_MODE

Single LED mode

Pulled high