Altera Cyclone V SoC Development Board User Manual

Page 16

2–8

Chapter 2: Board Components

MAX V CPLD 5M2210 System Controller

Cyclone V SoC Development Board

November 2013

Altera Corporation

Reference Manual

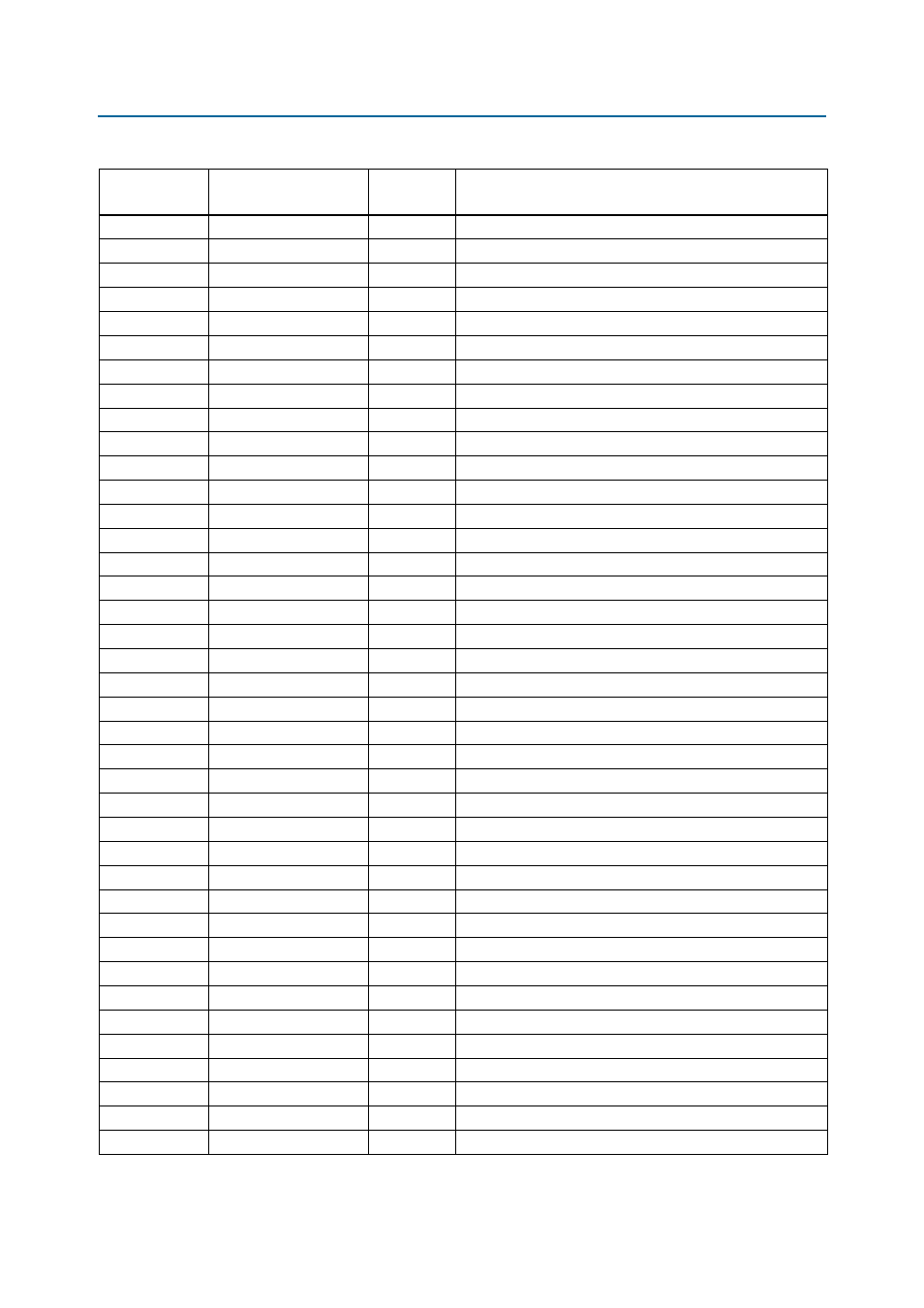

H14

FM_A18

1.8-V

FM address bus

H15

FM_A19

1.8-V

FM address bus

H13

FM_A20

1.8-V

FM address bus

H16

FM_A21

1.8-V

FM address bus

J13

FM_A22

1.8-V

FM address bus

J16

FM_A23

1.8-V

FM address bus

K12

FM_A24

1.8-V

FM address bus

M14

FM_A25

1.8-V

FM address bus

N13

FM_A26

1.8-V

FM address bus

J14

FM_D0

1.8-V

FM data bus

J15

FM_D1

1.8-V

FM data bus

K16

FM_D2

1.8-V

FM data bus

K13

FM_D3

1.8-V

FM data bus

K15

FM_D4

1.8-V

FM data bus

K14

FM_D5

1.8-V

FM data bus

L16

FM_D6

1.8-V

FM data bus

L11

FM_D7

1.8-V

FM data bus

L15

FM_D8

1.8-V

FM data bus

L12

FM_D9

1.8-V

FM data bus

M16

FM_D10

1.8-V

FM data bus

L13

FM_D11

1.8-V

FM data bus

M15

FM_D12

1.8-V

FM data bus

L14

FM_D13

1.8-V

FM data bus

N16

FM_D14

1.8-V

FM data bus

M13

FM_D15

1.8-V

FM data bus

K1

FPGA_CONF_DONE

2.5-V

FPGA configuration done LED

D3

FPGA_CONFIG_D0

2.5-V

FPGA configuration data

C2

FPGA_CONFIG_D1

2.5-V

FPGA configuration data

C3

FPGA_CONFIG_D2

2.5-V

FPGA configuration data

E3

FPGA_CONFIG_D3

2.5-V

FPGA configuration data

D2

FPGA_CONFIG_D4

2.5-V

FPGA configuration data

E4

FPGA_CONFIG_D5

2.5-V

FPGA configuration data

D1

FPGA_CONFIG_D6

2.5-V

FPGA configuration data

E5

FPGA_CONFIG_D7

2.5-V

FPGA configuration data

F3

FPGA_CONFIG_D8

2.5-V

FPGA configuration data

E1

FPGA_CONFIG_D9

2.5-V

FPGA configuration data

F4

FPGA_CONFIG_D10

2.5-V

FPGA configuration data

F2

FPGA_CONFIG_D11

2.5-V

FPGA configuration data

F1

FPGA_CONFIG_D12

2.5-V

FPGA configuration data

Table 2–4. MAX V CPLD System Controller Device Pin-Out (Part 2 of 4)

Board

Reference (U19)

Schematic Signal Name

I/O Standard

Description