Fpga programming using epcq, Status elements, Fpga programming using epcq –16 – Altera Cyclone V SoC Development Board User Manual

Page 24: Status elements –16

2–16

Chapter 2: Board Components

Status Elements

Cyclone V SoC Development Board

November 2013

Altera Corporation

Reference Manual

FPGA Programming using EPCQ

The EPCQ device with non-volatile memory features a simple six-pin interface and a

small form factor. The EPCQ supports AS x1 and x4 modes.

By default, this board has a FPP configuration scheme setting. The MAX_AS_CONF

pin needs to be driven from the MAX V to enable the bus switch (U13) to isolate the

EPCQ flash (U20) from the configuration bus. This happens when MSEL is 10010 or

10011.

In AS configuration scheme, the data will be read from the EPCQ flash directly to the

FPGA. The MAX V CPLD 5M2210 System Controller controls the nCS line of the

EPCQ to avoid line contention on DATA4 line due to functionality sharing. In order to

program non-volatile memory, CFI Flash or EPCQ special programming functionality

design should be loaded into the FPGA or MAX V CPLD to allow programming using

the Quartus II Programmer.

Status Elements

The development board includes status LEDs. This section describes the status

elements.

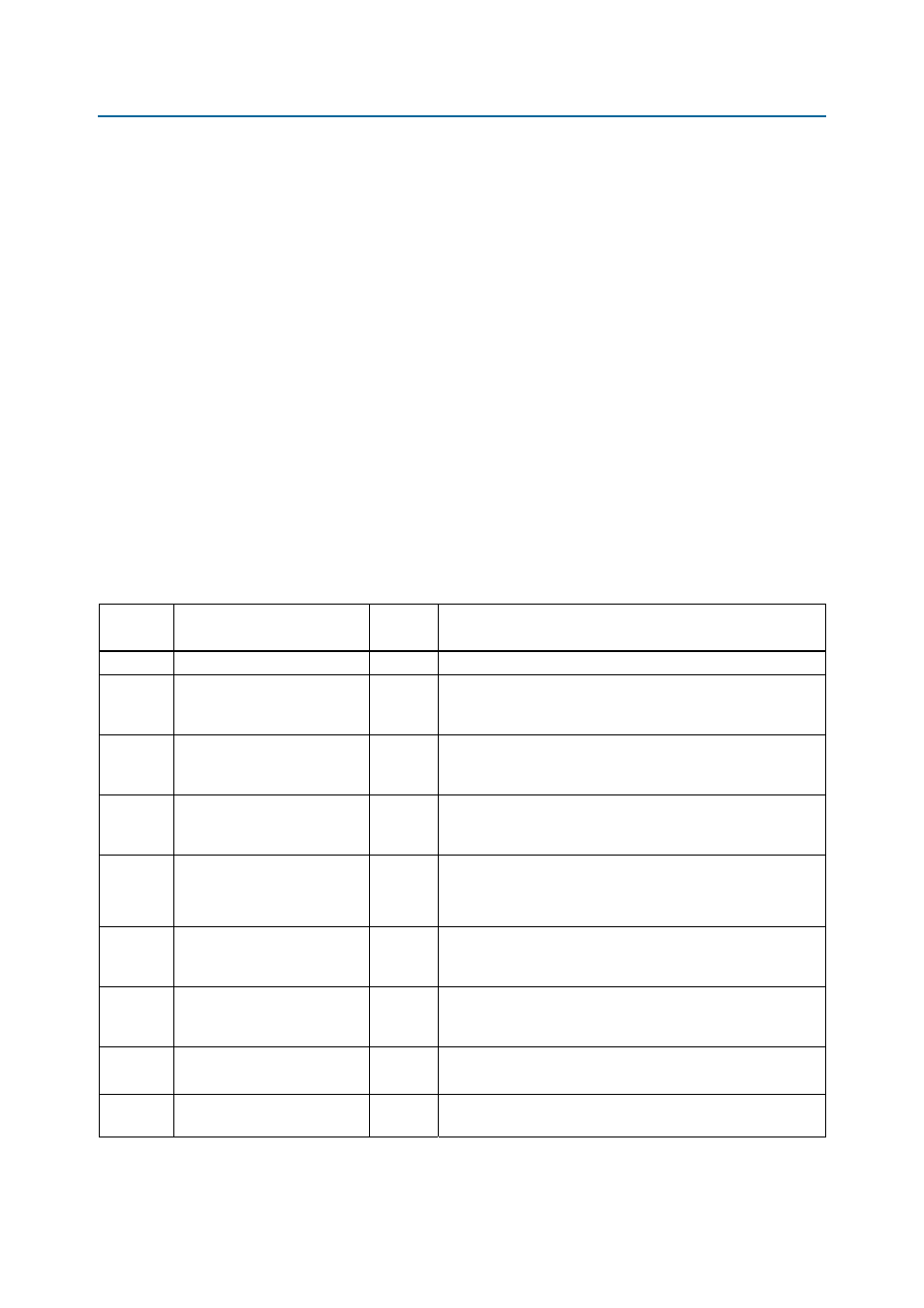

Table 2–7

lists the LED board references, names, and functional descriptions.

Table 2–7. Board-Specific LEDs

Board

Reference

Schematic Signal Name

I/O

Standard

Description

D35

Power

5.0-V

Blue LED. Illuminates when 5.0 V power is active.

D38

MAX_CONF_DONE

3.3-V

Green LED. Illuminates when the FPGA is successfully

configured. Driven by the MAX V CPLD 5M2210 System

Controller.

D36

MAX_ERROR

3.3-V

Red LED. Illuminates when the MAX V CPLD 5M2210 System

Controller fails to configure the FPGA. Driven by the MAX V

CPLD 5M2210 System Controller.

D34

MAX_LOAD

3.3-V

Green LED. Illuminates when the MAX V CPLD 5M2210 System

Controller is actively configuring the FPGA. Driven by the MAX V

CPLD 5M2210 System Controller.

D41

D40

D39

PGM_LED[0]

PGM_LED[1]

PGM_LED[2]

3.3-V

Green LEDs. Illuminates to indicate which hardware page loads

from flash memory when you press the PGM_SEL push button.

D37

CVP_CONF_DONE

2.5-V

Green LED. Illuminates when the FPGA is successfully

configured using CvP. Driven by the MAX V CPLD 5M2210

System Controller.

D9

HSMA_PRSNTn

2.5-V

Green LED. Illuminates when HSMC port A has a board or cable

plugged-in such that pin 160 becomes grounded. Driven by the

add-in card.

D30, D31

D29, D28

JTAG_RX, JTAG_TX

SC_RX, SC_TX

1.8-V

Green LEDs. Illuminates to indicate USB-Blaster II receive and

transmit activities.

D15, D14

UART_RX_LED, UART_TX_LED

3.3-V

Green LED. Illuminates to indicate UART receive and transmit

activities.