Features, Features –3 – Altera FIR Compiler User Manual

Page 7

Chapter 1: About the FIR Compiler

1–3

Features

© May 2011

Altera Corporation

■

Automatically generating the code required for the Quartus II software to

synthesize high-speed, area-efficient FIR filters of various architectures.

■

Generating a VHDL testbench for all architectures.

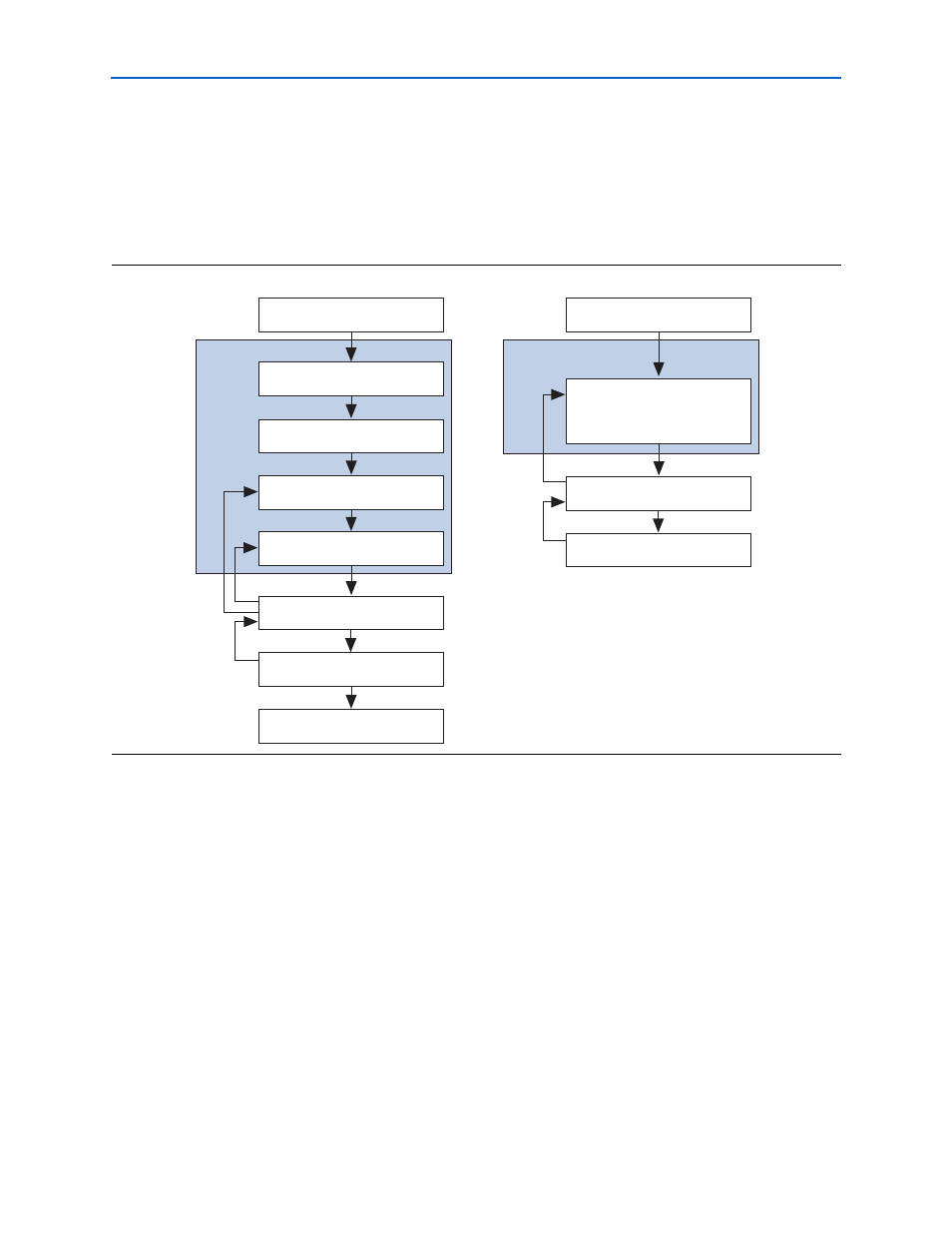

compares the design cycle using a FIR Compiler with a traditional

implementation.

Features

The Altera

®

FIR Compiler implements a finite impulse response (FIR) filter MegaCore

function and supports the following features:

■

The following hardware architectures are supported to enable optimal trade- offs

between logic, memory, DSP blocks, and performance:

■

Fully parallel distributed arithmetic

■

Fully serial distributed arithmetic

■

Multibit serial distributed arithmetic

■

Multicycle variable structures

■

Exploit maximal efficiency designs as a result of FIR Compiler hardware

optimizations such as interpolation, decimation, symmetry, decimation half-band,

and time sharing.

■

Easy system integration using Avalon

®

Streaming (Avalon-ST) interfaces.

Figure 1–3. Design Cycle Comparison

Define & Design Architectural

Blocks

Determine Behavioral

Characteristics of FIR Filter

Calculate Filter Coefficients

(MATLAB)

Determine Hardware Filter

Architecture

Design Structural or Synthesizable

FIR Filter

Simulate

Synthesize & Place & Route

Area/Speed Tradeoff

FIR Filter

Design

6 Weeks

Define & Design Architectural

Blocks

Simulate

Synthesize & Place & Route

FIR Filter Design

1 Day

Specify Filter Characteristics

to FIR Compiler Megafunction

(FIR Compiler Assists in Area/

Speed Tradeoff)

Traditional Flow

FIR Compiler Flow