Megacore verification, Performance and resource utilization – Altera FIR Compiler User Manual

Page 10

1–6

Chapter 1: About the FIR Compiler

MegaCore Verification

© May 2011

Altera Corporation

MegaCore Verification

Before releasing an updated version of the FIR Compiler, Altera runs a comprehensive

regression test to verify its quality and correctness.

All features and architectures are tested by sweeping all parameter options and

verifying that the simulation matches a master functional model.

Performance and Resource Utilization

This section shows typical expected performance for a FIR Compiler MegaCore

function with Cyclone III and Stratix IV devices. All figures are given for a FIR filter

with 97 taps, 8-bit input data, 14-bit coefficients, a target f

MAX

set to 1 GHz.

1

Cyclone III devices use combinational look-up tables (LUTs) and logic registers;

Stratix IV devices use combinational adaptive look-up tables (ALUTs) and logic

registers.

The resource and performance data was generated with the source ready signal

(

ast_source_ready

) always driven high, as described in

.

shows performance figures for Cyclone III devices:

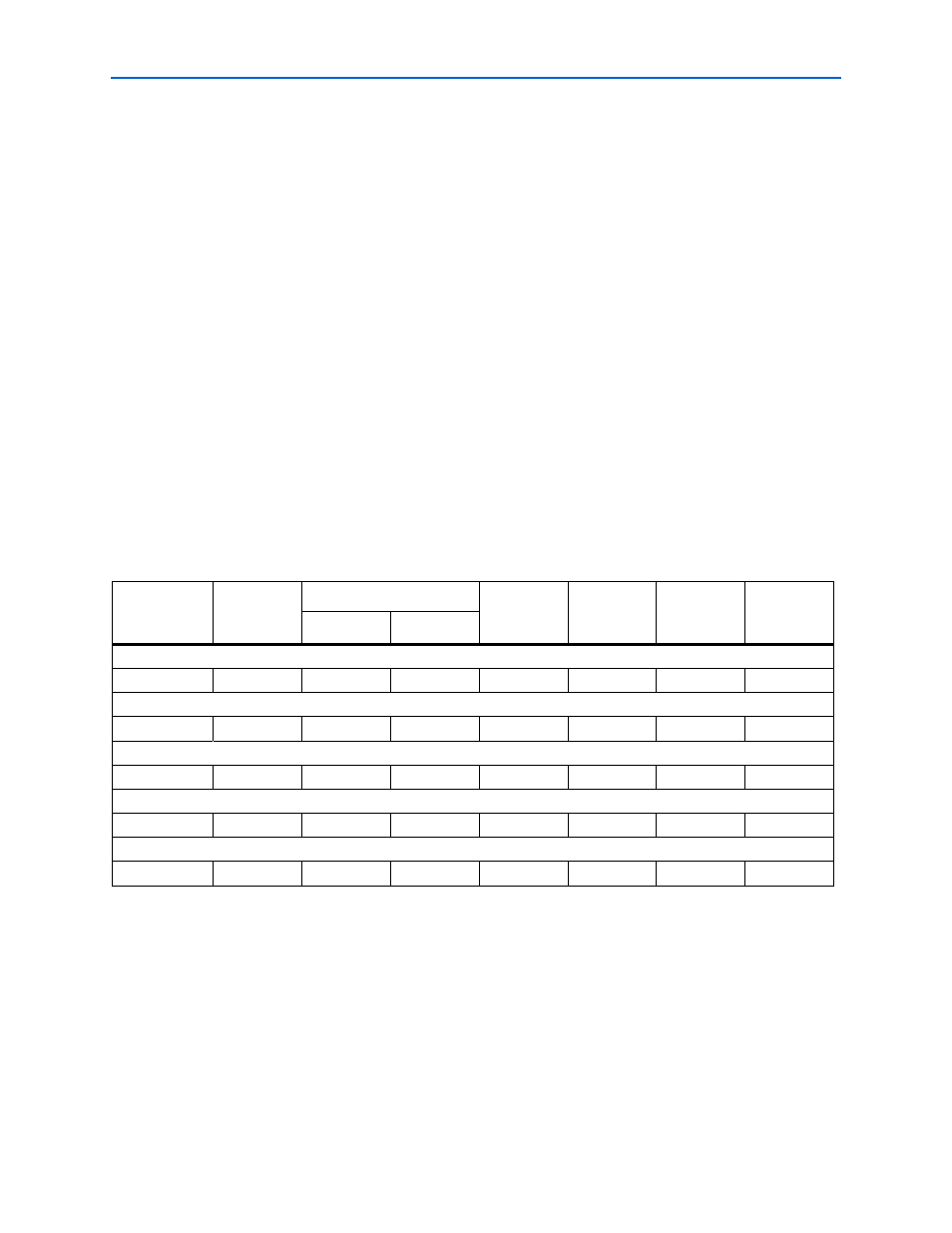

Table 1–5. FIR Compiler Performance—Cyclone III Devices (Part 1 of 2)

Combinational

LUTs

Logic

Registers

Memory

Multipliers

(9x9)

f

max

(MHz)

Throughput

(MSPS)

Processing

Equivalent

(GMACs)

Bits

M9K

Multibit Serial, pipeline level 1

899

1,331

55,148

31

—

310

62

6

Multicycle variable (1 cycle) decimation by 4, pipeline level 1

857

1,336

1,158

12

26

281

281

27

Multicycle variable (1 cycle) interpolation by 4, pipeline level 2

1,528

2,657

66

1

50

290

290

28

Multicycle variable (1 cycle), pipeline level 2

,

2,543

4,837

92

1

98

280

280

27

Multicycle variable (4 cycle), pipeline level 2

,

1,182

1,715

578

9

26

283

71

7