Symmetrical architecture selection, Symmetrical serial – Altera FIR Compiler User Manual

Page 45

Chapter 4: Functional Description

4–3

FIR Compiler

© May 2011

Altera Corporation

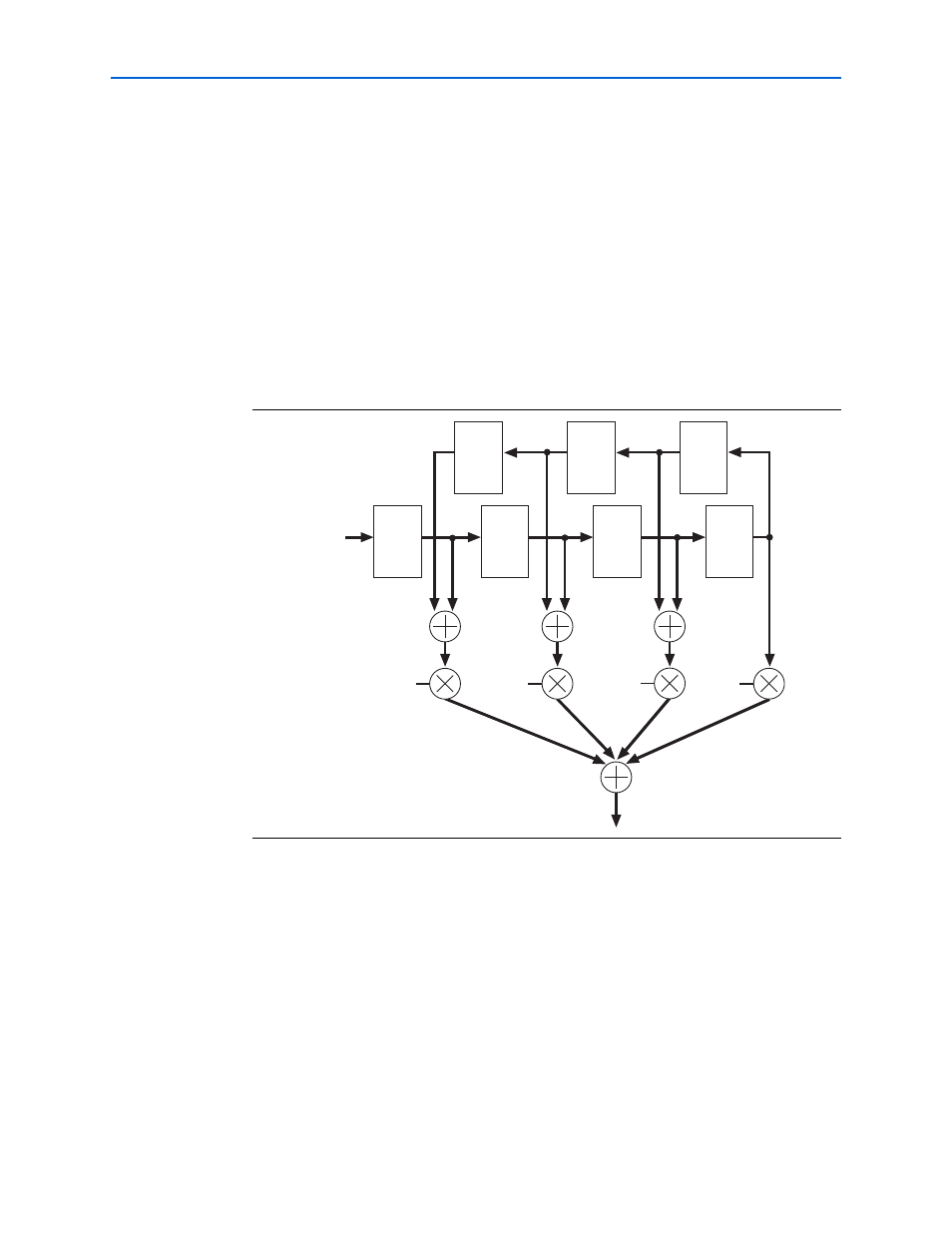

Symmetrical Architecture Selection

Many FIR filters have symmetrical coefficient values. The FIR Compiler examines the

coefficients and automatically determines the filter’s symmetry: even, odd, or none.

After detecting symmetry, the wizard selects an optimum algorithm to minimize the

amount of computation needed. The FIR compiler determines coefficient symmetry

after the coefficients are rounded. If symmetry is present, two data points are added

prior to the multiplication step, saving a multiplication operation (taking advantage

of filter symmetry reduces the number of multipliers by about half).

1

The wizard gives you the option to force non-symmetrical structures. If the

symmetry-optimized architecture is not available, this option is disabled.

Odd and even filter structures are shown in

and

.

Symmetrical Serial

Symmetrical serial filters take an additional clock cycle to perform the FIR

computation (so the filter can compute the carry). Additional logic cells are required

for the symmetrical adder resources.

Because non-symmetrical serial FIR filters do not require this resource, non-

symmetrical filters may be smaller and/or faster.

You can use the Resource Estimator in the Architecture Specification area of the

Parameterize FIR Compiler

page to determine the best solution available. Refer to

).

Figure 4–1. Seven-Tap Symmetrical FIR Filter

Data In

Data Out

Z

-1

C

0

Z

-1

C

1

C

2

C

3

Z

-1

Z

-1

Z

-1

Z

-1

Z

-1