Altera FIR Compiler User Manual

Page 67

Chapter 4: Functional Description

4–25

Timing Diagrams

© May 2011

Altera Corporation

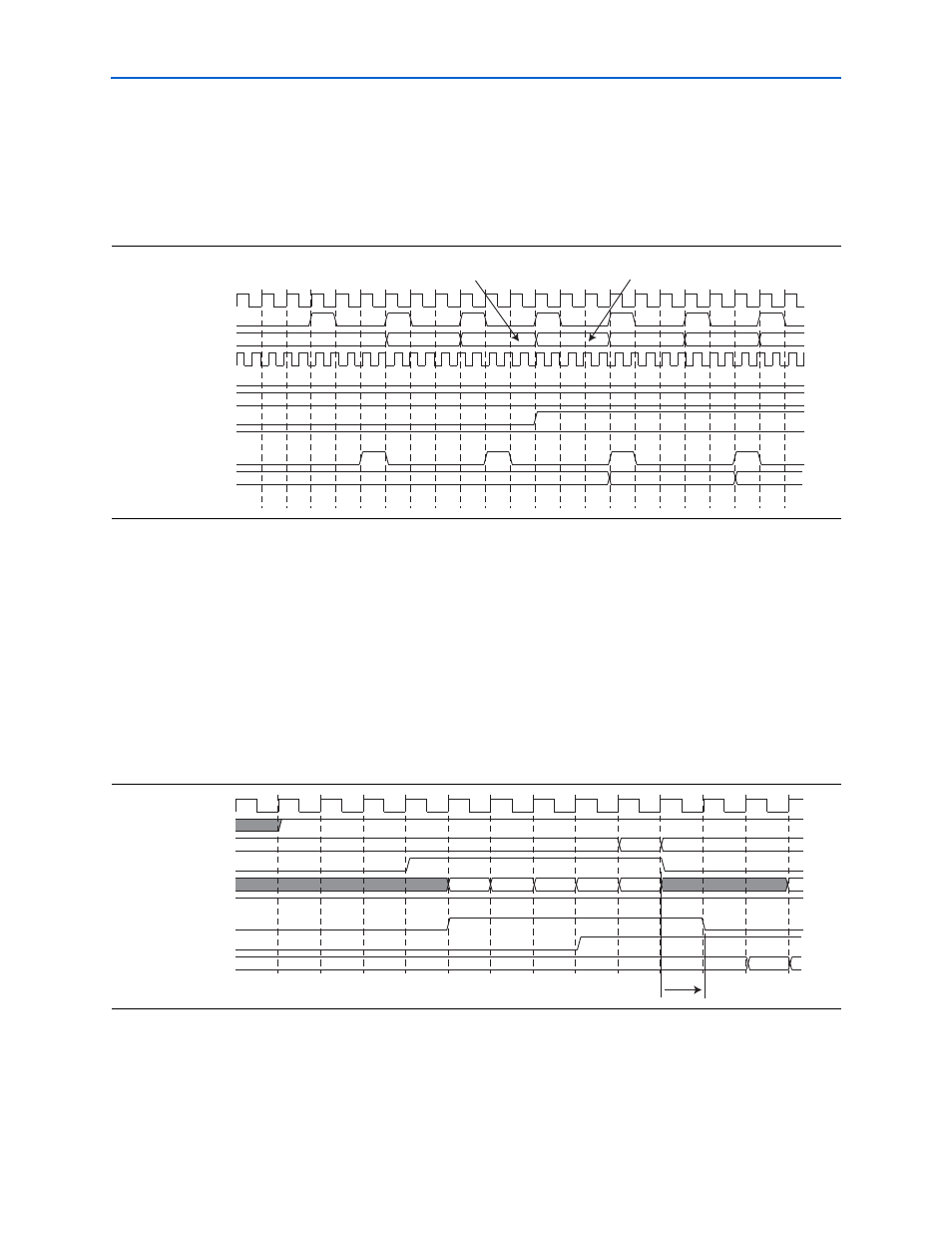

The selection of the coefficient set for calculation is also not synchronous to the input

data because of the Avalon-ST flow controller. Once the

coef_set

signal is set to a

particular value, it immediately affects the operation of the filter. This means that

some of the input data already received by the Avalon-ST controller will be calculated

using the new coefficient set (

1

For DSP Builder users, a button is available that ties the

coef_in_clk

to the

clk

in

the wrapper. DSP Builder will not work with more than one clock domain per

MegaCore function.

When loading multiple coefficient sets, to identify the coefficient set being loaded, the

duration of the clock cycle for coef_set_in must be one clock cycle longer than the

duration of coef_we as shown in

These timing requirements affect all designs that load multiple coefficient sets. If the

specified timing requirements are not met when loading multiple coefficient sets, a

specific set of coefficients will not be identified.

Figure 4–28. Multiple Coefficient Set Selection Timing Diagram

clk

ast_sink_ready

ast_sink_data

coef_in_clk

coef_we

coef_in

coef_set

coef_set_in

ast_source_valid

ast_source_data

0

113

-69

26

73

-56

-56

0

0

-791

82

This data is calculated

with coef_set1

Due to Avalon-ST buffering, this and some of the previous

data values can also be calculated with coef_set1.

Figure 4–29. Timing Requirements for Loading Multiple Coefficient Sets

clk

ast_sink_ready

ast_sink_data

coef_we

coef_in

coef_set

coef_set_in

ast_source_valid

ast_source_data

0

1

0

1

0

18

-2

-7

-1

0

0

0

18

coef_set_in must be sustained one clock cycle longer than coef_we