Altera JESD204B IP User Manual

Page 86

requires a read-modify-write operation (read first, then write), in such a way that it modifies only the

appropriate bits in a register and not changing other bits.

In the design example, MIF approach is used to reconfigure the ATX PLL and transceiver channel in the

JESD204 IP core via the Transceiver Reconfiguration Controller. The number of reconfiguration interface

is determined by number of lanes (L) + number of TX_PLL (different number of TX_PLL for bonded and

non-bonded mode). Since the MIF approach reconfiguration for transceiver only supports non-bonded

mode, the number of TX_PLL is equal to number of lanes. The number of reconfiguration interface = 2 x

number of lanes (L).

The transceiver reconfiguration controller interfaces:

• MIF Reconfiguration Avalon-MM master interface—connects to the MIF ROM.

• Transceiver Reconfiguration interface—connects to the JESD204B IP core, which eventually connects

to the native PHY.

• Reconfiguration Management Avalon-MM slave interface—connects to the control unit.

Note: The transceiver reconfiguration controller is only used in Arria V and Stratix V devices. For Arria

10 devices, the control unit directly communicates with the transceiver in the JESD204B IP core

through the

reconfig_avmm_*

interface signals.

The following transceiver reconfiguration controller Avalon-MM operations are involved during data rate

reconfiguration.

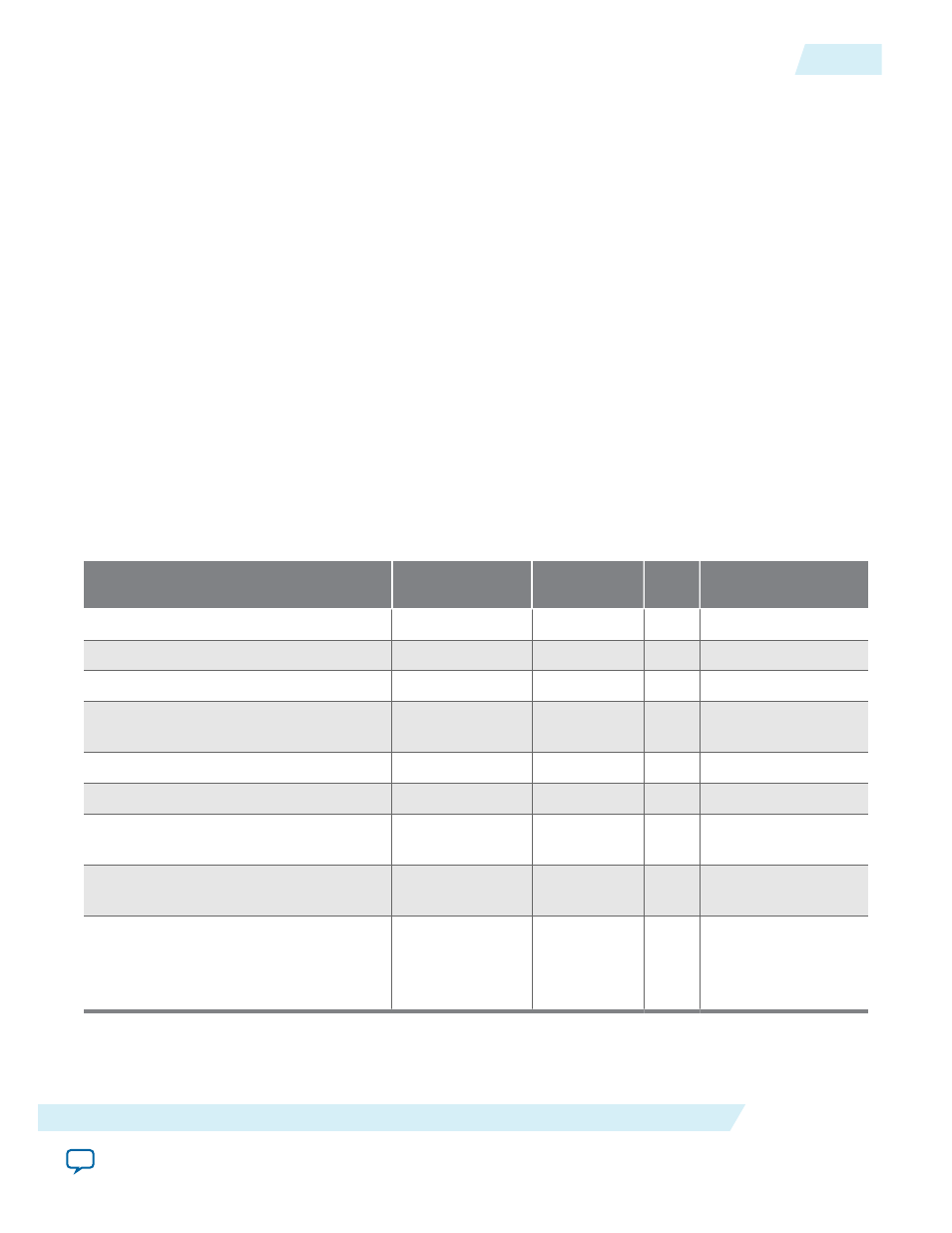

Table 5-2: Transceiver Reconfiguration Controller Operation for Arria V and Stratix V Devices

Operation

Avalon-MM

Interface Signal

Byte Address

Offset (6bits)

Bit

Value

Write logical channel number

reconfig_mgmt_* 0x38

[9:0]

0

Write MIF mode

reconfig_mgmt_* 0x3A

[3:2]

2'b00

Write 0 to streamer offset register

reconfig_mgmt_* 0x3B

[15:0] 0

Write MIF base address to streamer

data register

reconfig_mgmt_* 0X3C

[31:0] *32'h1000

Initiate a write of all the above data

reconfig_mgmt_* 0x3A

[0]

1'b1

Write 1 to streamer offset register

reconfig_mgmt_* 0x3B

[15:0] 1

Write to streamer data register to set up

MIF streaming

reconfig_mgmt_* 0x3C

[31:0] 3

Initiate a write of all the above data to

start streaming the MIF

reconfig_mgmt_* 0x3A

[0]

1'b1

Read the busy bit to determine when

the write has completed

reconfig_mgmt_* 0x3A

[8]

1: Busy

0: Operation

completed

Note: The above steps are repeated for the number of channels and followed by the number of TX_PLLs.

UG-01142

2015.05.04

Transceiver Reconfiguration Controller

5-5

JESD204B IP Core Design Guidelines

Altera Corporation