Altera JESD204B IP User Manual

Page 122

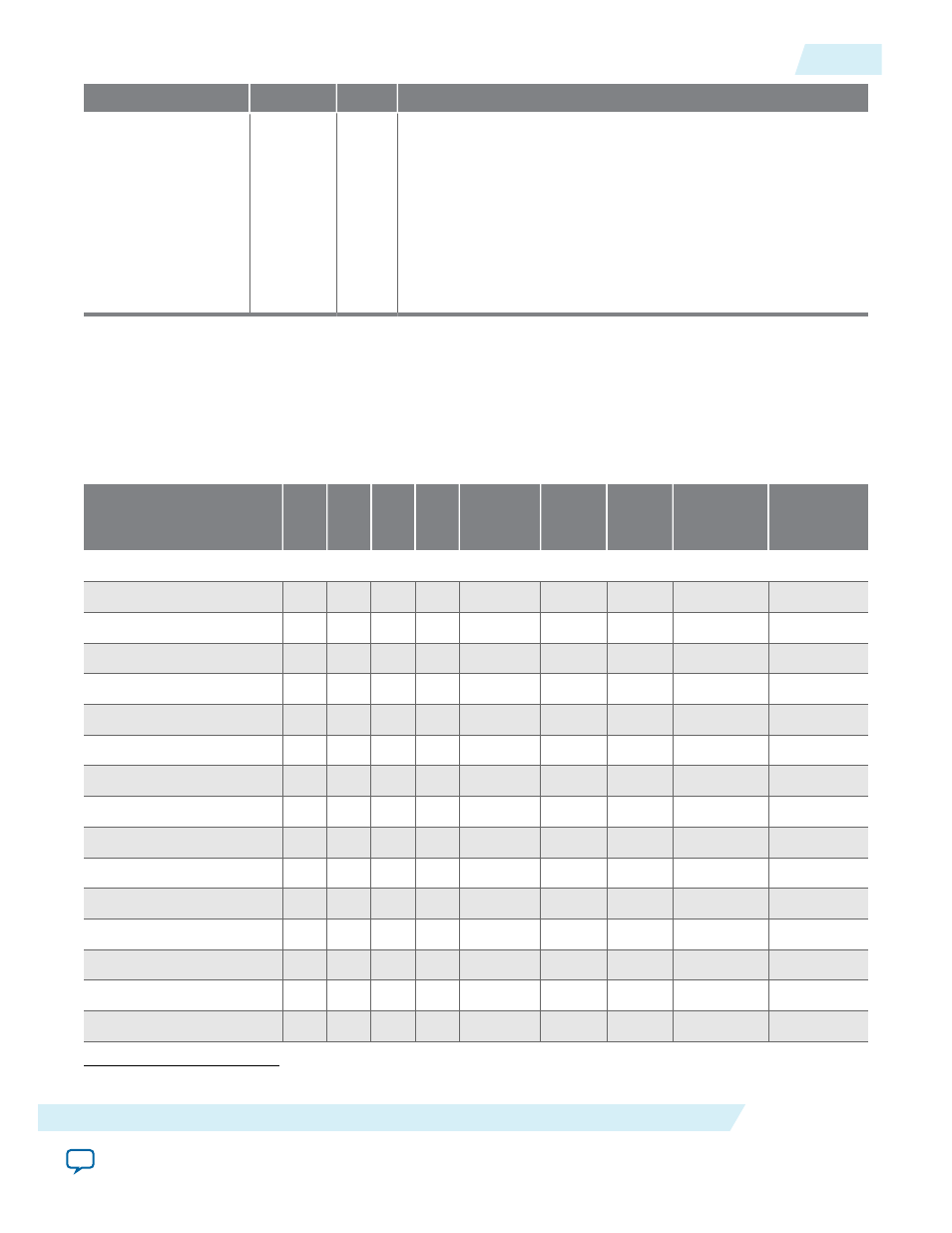

Parameter

Value

(37)

Default

Description

FEEDBACK_TAP 6, 5, 14, 18,

28

6

Defines the feedback tap for the PRBS pattern generator and

checker. This is an intermediate stage that is XOR-ed with the

last stage to generate to next PRBS bit.

• If PRBS-7 is required, set this parameter to 6.

• If PRBS-9 is required, set this parameter to 5.

• If PRBS-15 is required, set this parameter to 14.

• If PRBS-23 is required, set this parameter to 18.

• If PRBS-31 is required, set this parameter to 28.

Table below lists the configuration that this design example supports. However, the design example

generated by the Qsys system is always fixed at a data rate of 6144 Mbps and a limited set of configuration

as shown in the table below. If your setting in the Qsys parameter editor does not match one of the LMF

and bonded mode parameter values in

Table

, the design example is generated with the default values of

LMF = 124.

Table 5-19: Static and Dynamic Reconfiguration Parameter Values Supported

Mode

Link

L

M

F

Reference

Clock

Frame

Clock

Link

Clock

F1_

FRAMECLK_

DIV

F2_

FRAMECLK_

DIV

Static

Bonded/Non-bonded

2

1

1

2

153.6

153.6

153.6

2

Bonded/Non-bonded

1

1

1

4

153.6

153.6

153.6

1

Bonded/Non-bonded

1

1

2

4

153.6

153.6

153.6

1

Bonded/Non-bonded

1

1

4

8

153.6

76.8

153.6

1

Bonded/Non-bonded

1

2

1

1

153.6

153.6

153.6

4

Bonded/Non-bonded

1

2

1

2

153.6

153.6

153.6

2

Bonded/Non-bonded

1

2

1

4

153.6

153.6

153.6

1

Bonded/Non-bonded

2

2

2

2

153.6

153.6

153.6

2

Bonded/Non-bonded

1

2

2

4

153.6

153.6

153.6

1

Bonded/Non-bonded

1

2

4

4

153.6

153.6

153.6

1

Bonded/Non-bonded

1

4

2

1

153.6

153.6

153.6

4

Bonded/Non-bonded

1

4

2

2

153.6

153.6

153.6

2

Bonded/Non-bonded

1

4

4

2

153.6

153.6

153.6

2

Bonded/Non-bonded

1

4

4

4

153.6

153.6

153.6

1

Bonded/Non-bonded

1

4

8

4

153.6

153.6

153.6

1

(37)

Values supported or demonstrated by this design example.

UG-01142

2015.05.04

System Parameters

5-41

JESD204B IP Core Design Guidelines

Altera Corporation