Altera JESD204B IP User Manual

Page 7

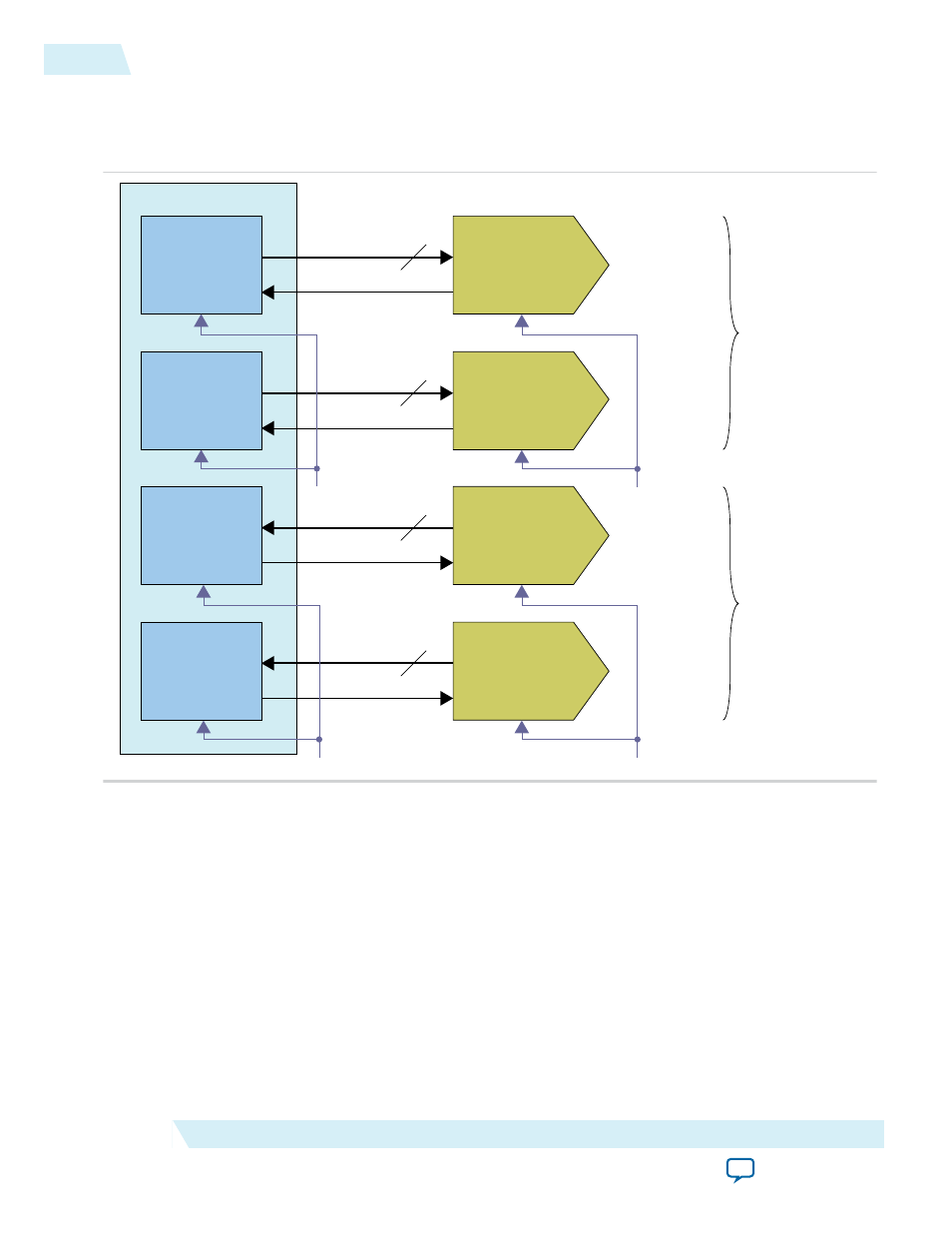

Figure 2-1: Typical System Application for JESD204B IP Core

The JESD204B IP core utilizes the Avalon-ST source and sink interfaces, with unidirectional flow of data,

to transmit and receive data on the FPGA fabric interface.

JESD204B TX

IP Core

FPGA

M Converters

1 Link, L Lanes

SYNC_N

M Converters

M Converters

SYNC_N

SYNC_N

M Converters

SYNC_N

JESD204B RX

IP Core

1 Link, L Lanes

1 Link, L Lanes

1 Link, L Lanes

DAC Device

Clock 1

ADC Device

Clock 1

Multi-Device

Synchronization

through Subclass 1

or Subclass 2

Multi-Device

Synchronization

through Subclass 1

or Subclass 2

Logic Device (TX)

Device Clock 2

Logic Device (RX)

Device Clock 2

JESD204B TX

IP Core

JESD204B RX

IP Core

Key features of the JESD204B IP core:

• Data rate of up to 12.5 Gbps

• Run-time JESD204B parameter configuration (L, M, F, S, N, K, CS, CF)

• MAC and PHY partitioning for portability

• Subclass 0 mode for backward compatibility to JESD204A

• Subclass 1 mode for deterministic latency support (using SYSREF) between the ADC/DAC and logic

device

• Subclass 2 mode for deterministic latency support (using SYNC_N) between the ADC/DAC and logic

device

• Multi-device synchronization

2-2

About the JESD204B IP Core

UG-01142

2015.05.04

Altera Corporation

About the JESD204B IP Core