Tx error reporting – Altera JESD204B IP User Manual

Page 104

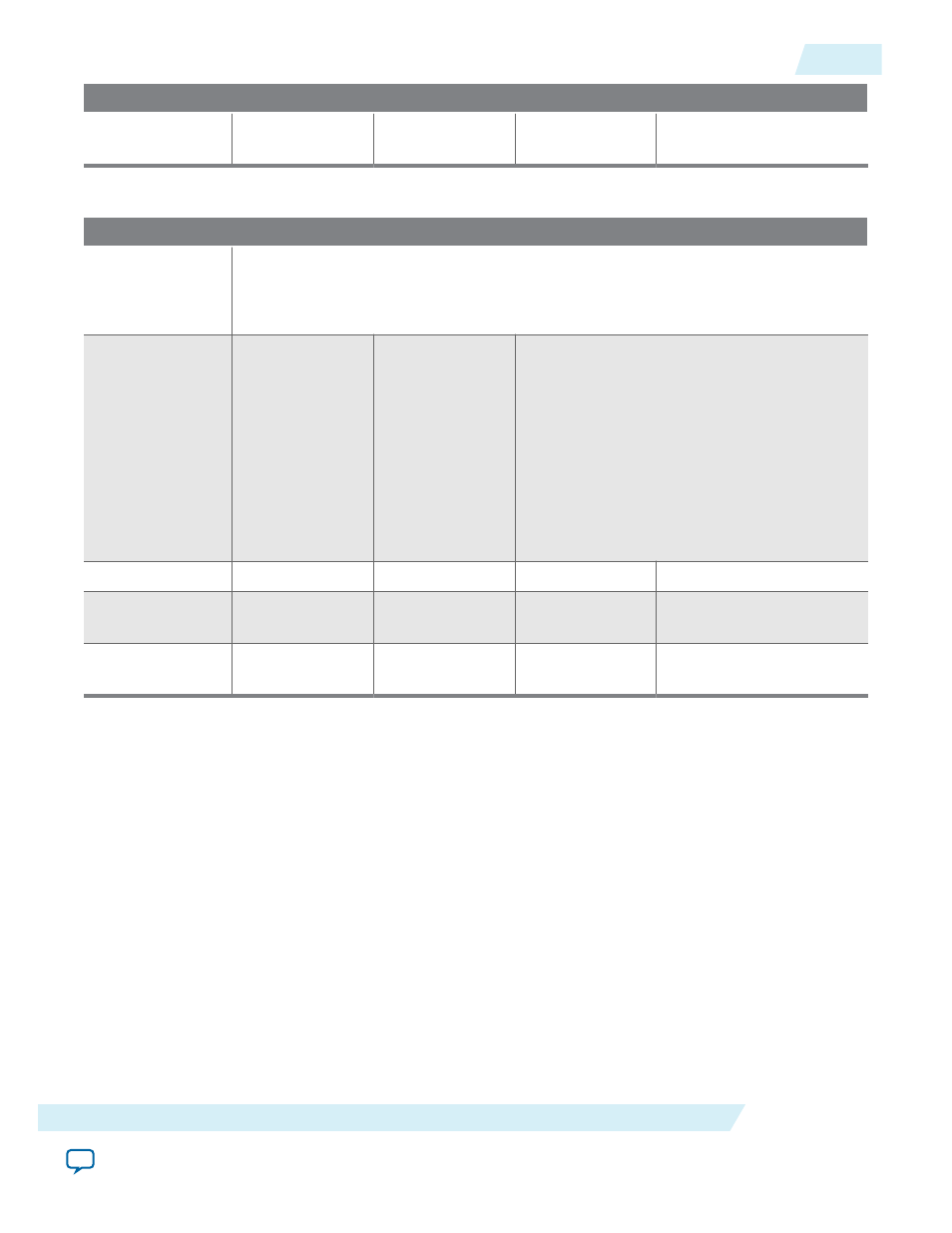

F = 4

Data Out

{F12, F13, F14,

F15}

{F8, F9, F10, F11} {F4, F5, F6, F7}

{F0, F1, F2, F3}

Table 5-9: Data Mapping for F=8, L=4

F = 8

Supported M

and S

M*S=16 for F=8, L=4

F=8 supports either (case1: M=1, S=16), (case2: M=2, S=8), (case3: M=4, S=4), (case4:

M=8, S=2) or (case5: M=16, S=1)

F=8

jesd204_tx_

datain[255:0] =

{{F3031,

F28F29,F26F27,

F24F25}, {F22F23,

F20F21,F18F19,

F16F17}, {F14F15,

F12F13,F10F11,

F8F9}, {F6F7,F4F5,

F2F3,F0F1}}

Case1: M=1, S=16 {M0S15, M0S14, M0S13, M0S12, M0S11,

M0S10, M0S9, M0S8, M0S7, M0S6, M0S5,

M0S4, M0S3, M0S2, M0S1, M0S0}

Lane

L3

L2

L1

L0

Data Out at

linkclk T0

{F24, F25, F26,

F27}

{F16, F17, F18,

F19}

{F8, F9, F10, F11} {F0, F1, F2, F3}

Data Out at

linkclk T1

{F28, F29, F30,

F31}

{F20, F21, F22,

F23}

{F12, F13, F14,

F15}

{F4, F5, F6, F7}

TX Error Reporting

For TX path error reporting, the transport layer expects a valid stream of TX data from the Avalon-ST

interface (indicated by

jesd204_tx_data_valid

signal = 1) as long as the

jesd204_tx_data_ready

remains asserted. If the

jesd204_tx_data_valid

signal unexpectedly deasserts during this stage, the

transport layer reports an error to the DLL by asserting the

jesd204_tx_link_error

signal and

deasserting the

jesd204_tx_link_data_valid

signal accordingly, as shown in the timing diagram below.

UG-01142

2015.05.04

TX Error Reporting

5-23

JESD204B IP Core Design Guidelines

Altera Corporation