Transmitter, Transmitter -4 – Altera JESD204B IP User Manual

Page 41

Avalon-MM Interface

The Avalon-MM slave interface provides access to internal CSRs. The read and write data width is 32-bits

(DWORD access). The Avalon-MM slave is asynchronous to the

txlink_clk

,

txframe_clk

,

rxlink_clk

,

and

rxframe_clk

clock domains. You are recommended to release the reset for the CSR configuration

space first. All run-time JESD204B configurations like L, F, M, N, N', CS, CF, and HD should be set before

releasing the reset for link and frame clock domain.

Each write transfer has a writeWaitTime of 0 cycle while a read transfer has a readWaitTime of 1 cycle and

readLatency of 1 cycle.

Related Information

More information about the Avalon-ST and Avalon-MM interfaces, including timing diagrams.

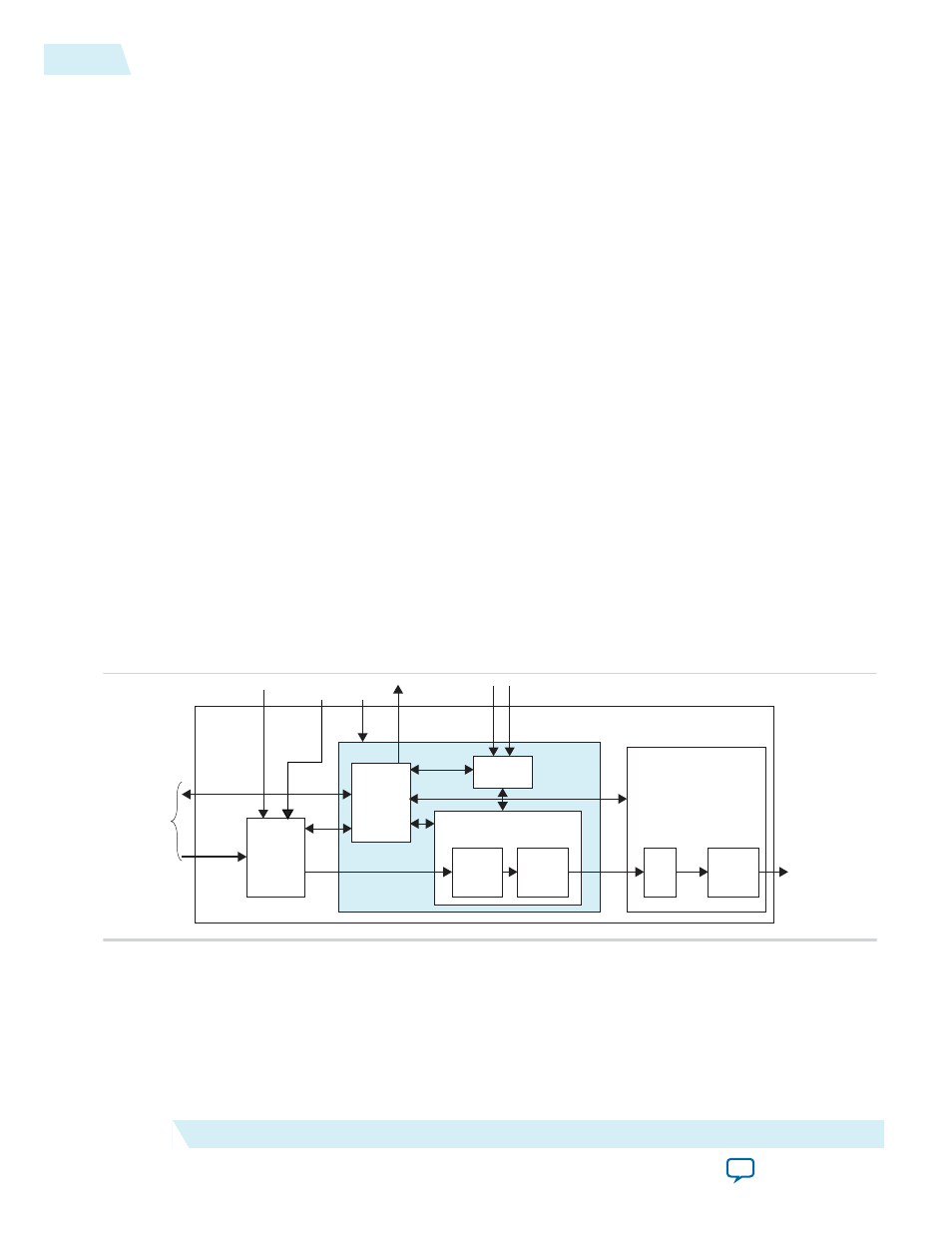

Transmitter

The transmitter block, which interfaces to DAC devices, takes one of more digital sample streams and

converts them into one or more serial streams.

The transmitter performs the following functions:

• Data scrambling

• Frame or lane alignment

• Character generation

• Serial lane monitoring

• 8B/10B encoding

• Data serializer

Figure 4-3: Transmitter Data Path Block Diagram

TX Frame

Deassembly

Per Device

TX CSR

Per Device

TX CTL

Per Device

Scrambler

Data Link

Layer (TX)

Soft

PCS

(TX)

Hard PCS

and

Transceiver

JESD204B

(TX) Per Device

CSR

CSR

CSR

32 Bit PCS

Per Channel

Transceiver (TX)

Per Device

SYNC_N

SYSREF

TX_INT

TXLINK_CLK

TXFRAME_CLK

Avalon-MM

Avalon-ST

To Avalon

Interface

Bus

JESD204 TX Transport Layer with

Base and Transceiver Design Example

Avalon-ST

32 Bits per Channel

Serial Interface

(TX_n, TX_p)

The transmitter block consists of the following modules:

4-4

Transmitter

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Functional Description